9022fc2

Caliptra Subsystem Integration Specification

Version 2.0.1

- Scope

- Overview

- Caliptra Subsystem High level diagram

- Integration Considerations

- Verification View of Caliptra Subsystem

- Caliptra Subsystem Top

- Caliptra Core

- MCU (Manufacturer Control Unit)

- Fuse Controller

- Fuse Controller Macro

- Life Cycle Controller

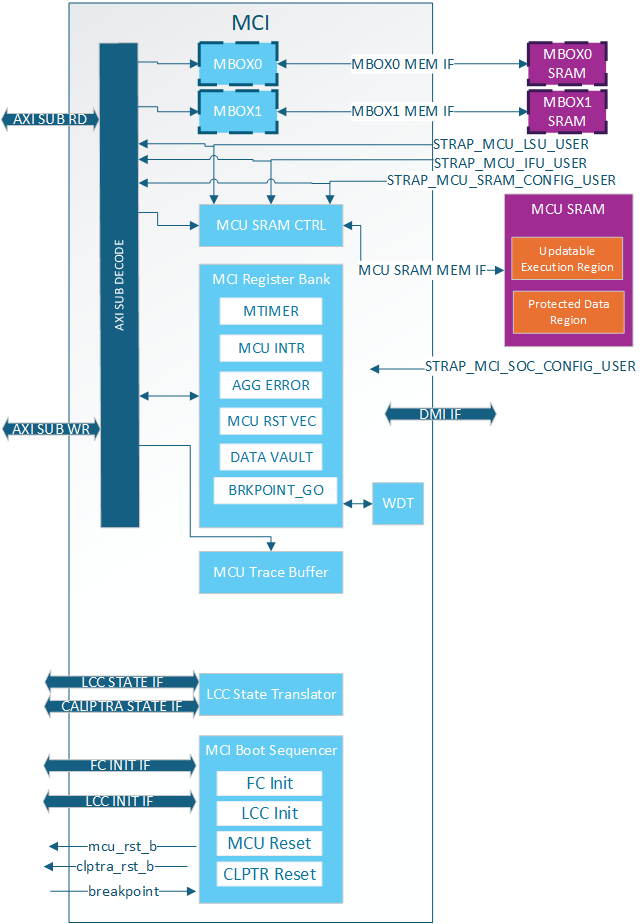

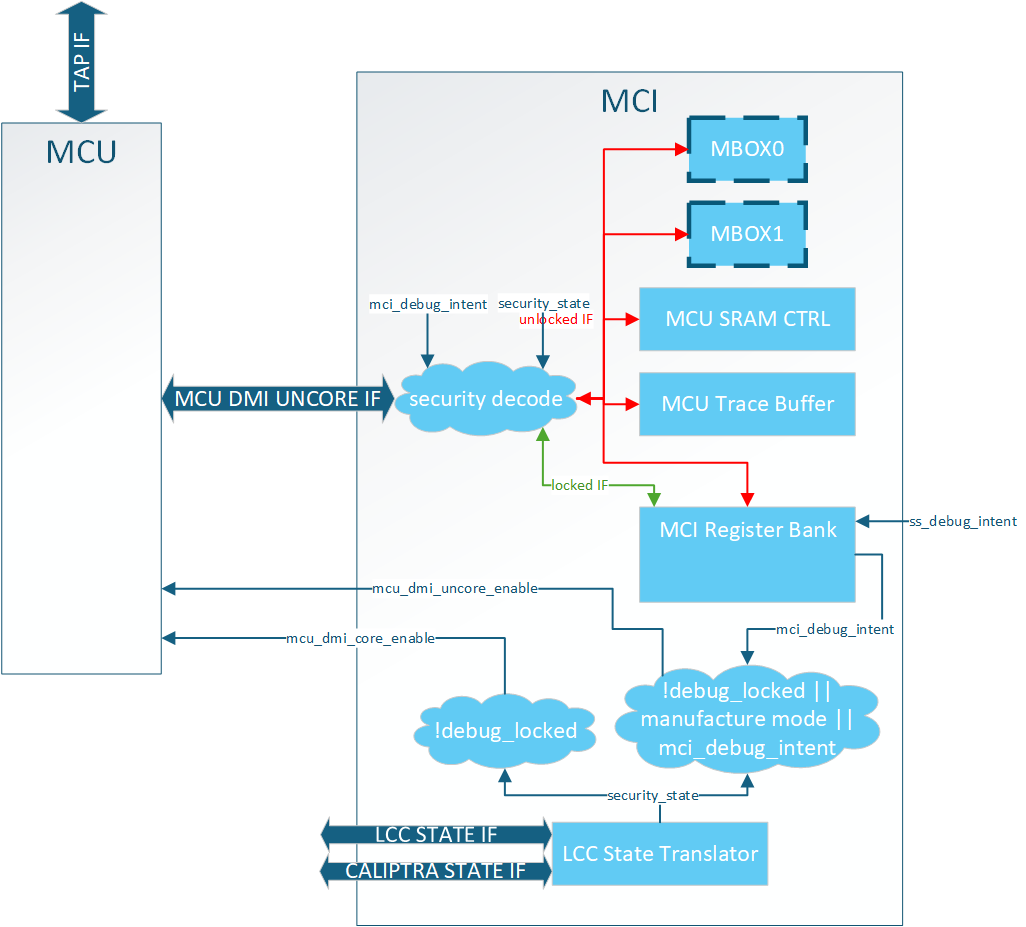

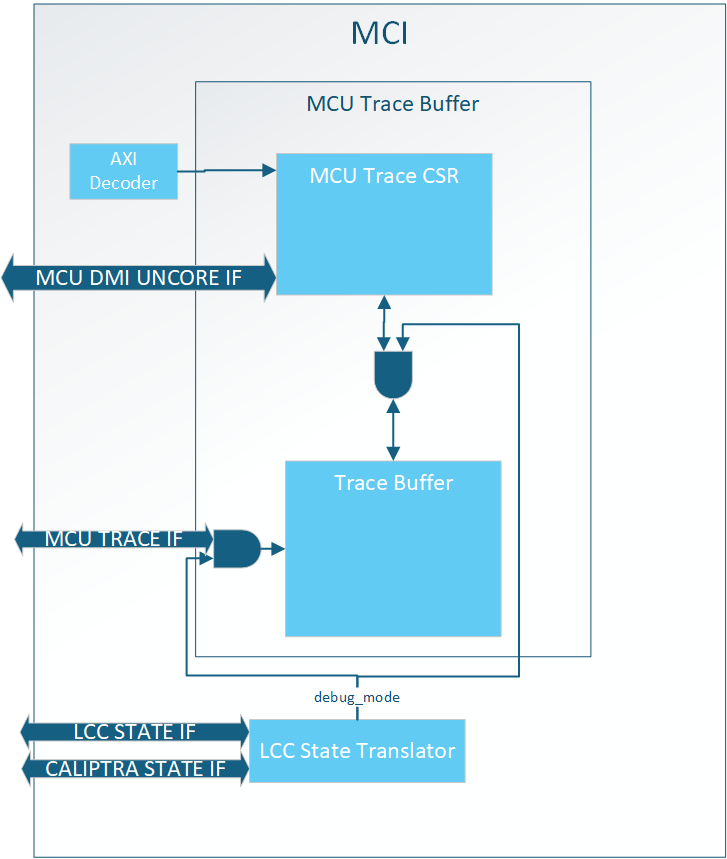

- MCI

- Overview

- Parameters & Defines

- Interface

- Memory Map / Address map

- MCI Integration Requirements

- Error Aggregation Connectivity Requirements

- Subsystem Internal Fuse Controller Initialization Connectivity Requirements

- Subsystem Internal Life Cycle Controller Initialization Connectivity Requirements

- MCI MCU Connectivity Requirements

- MCI Caliptra Core Connectivity Requirements

- LCC Gasket Connectivity Requirements

- MCU SRAM Sizing Requirements

- MCU MBOX SRAM Sizing Requirements

- Programming interface

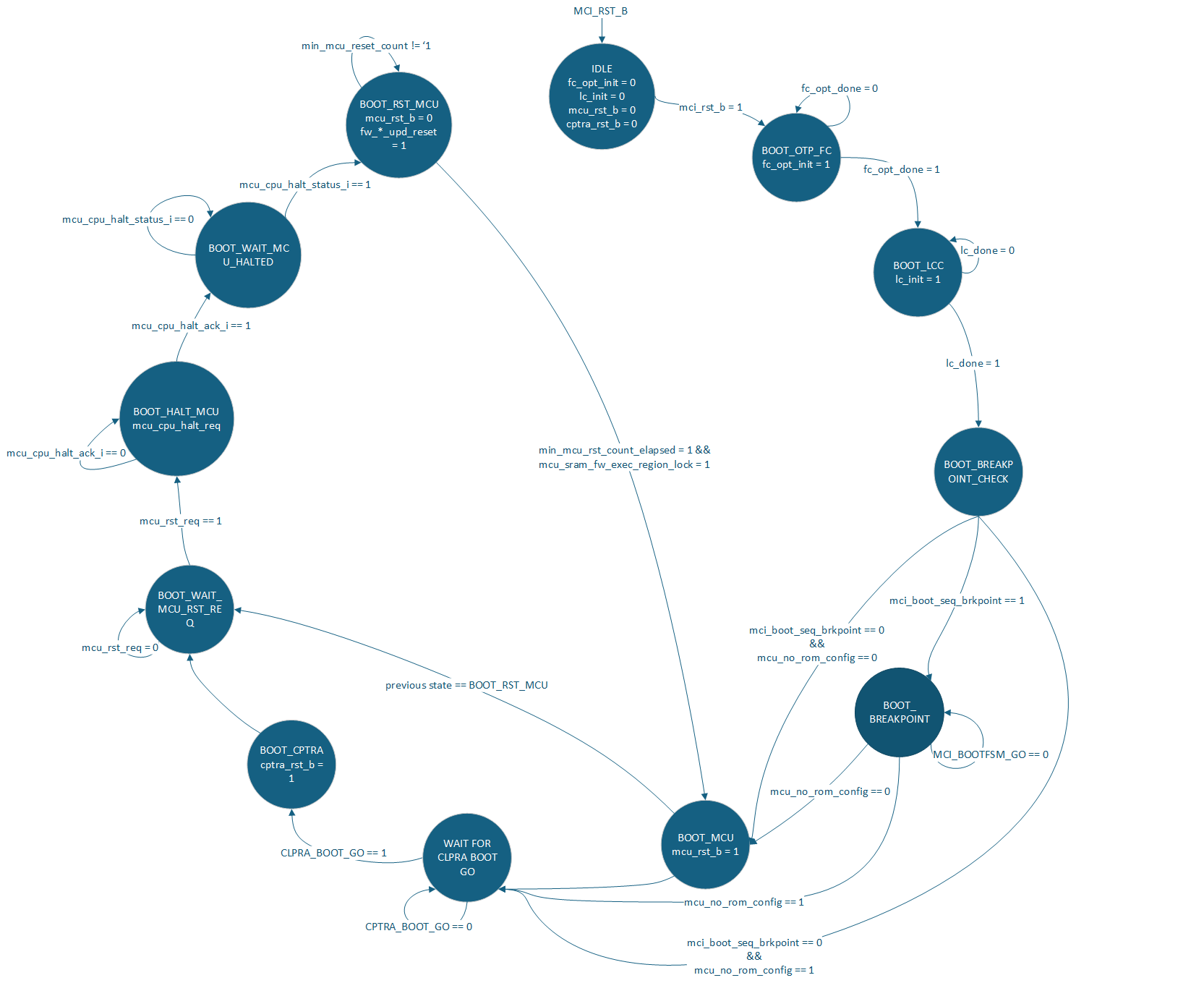

- Sequences : Reset, Boot,

- Other requirements

- I3C core

- CDC analysis and constraints

- Reset Domain Crossing

- Synthesis

- Terminology

Scope

For Caliptra Subsystem, this document serves as a hardware integration specification. The scope of this document is to assist integrators in the integration of Caliptra Subsystem. It is not intended to serve as a hardware specification or to include micro-architectural details. This document includes Caliptra Subsystem top-level details along with parameters, defines, interfaces, memory map, programming reference, and guidelines on how to test the integration of the design.

Document Version

| Date | Document Version | Description |

|---|---|---|

| Jan 31st, 2025 | v0p8 | Work in progress |

| Apr 30th, 2025 | v1p0-rc1 | Initial release candidate of Caliptra Gen 2.0 Subsystem Documents. Specifcations updated with: - Detail on usage of all Subsystem flows such as Streaming Boot, Mailbox operation, and Debug Unlock - Details on design connectivity with top-level ports - Requirements and recommendations for integrators when adding Caliptra Subsystem to SoC designs |

Related repositories & specifications

The components described in this document are either obtained from open-source GitHub repositories, developed from scratch, or modified versions of open-source implementations. Links to relevant documentation and GitHub sources are shared in the following table.

Table 1: Related specification and repositories

| IP/Block | Code (GitHub URL) | Documentation (URL) |

|---|

| Caliptra | GitHub - chipsalliance/Caliptra| Caliptra Gen 2.0 Specification | Caliptra-SS | GitHub - chipsalliance/caliptra-ss| Hardware Specification Document | Caliptra-rtl | GitHub - chipsalliance/caliptra-rtl | Caliptra RTL documentation | | Cores-VeeR | GitHub - chipsalliance/Cores-VeeR-EL2 | VeeR EL2 Programmer’s Reference Manual | | I3C-Core | GitHub - chipsalliance/i3c-core | I3C core documentation | | Adams Bridge | GitHub - chipsalliance/adams-bridge | Adams Bridge Documentation |

Overview

The Caliptra Subsystem is designed to provide a robust Root of Trust (RoT) for datacenter-class System on Chips (SoCs), including CPUs, GPUs, DPUs, and TPUs. It integrates both hardware and firmware components to deliver essential security services such as identity establishment, measured boot, and attestation. By incorporating the Caliptra Subsystem, integrators can enhance the security capabilities of their SoCs, providing a reliable RoT that meets industry standards and addresses the evolving security needs of datacenter environments.

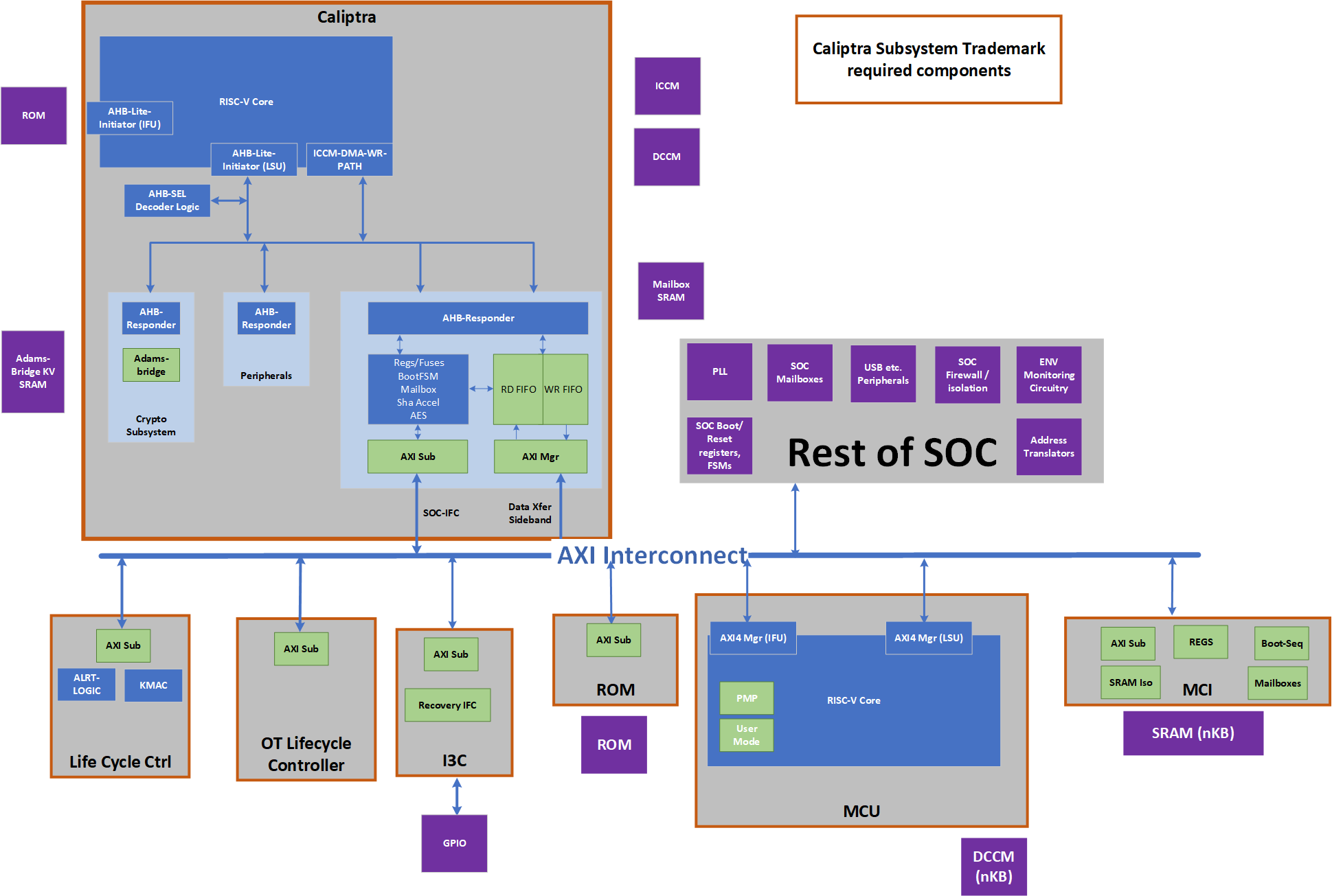

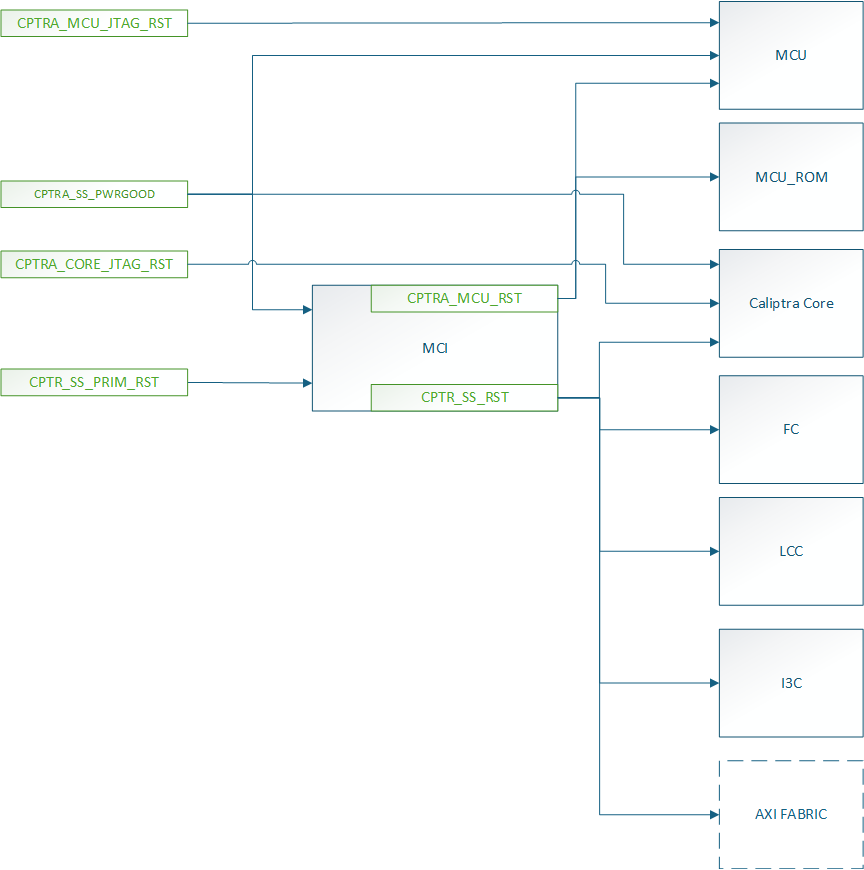

Caliptra Subsystem High level diagram

The following diagram provides a high-level overview of the Caliptra subsystem. It illustrates the key components and their interconnections within the system. For an in-depth understanding of the Caliptra Subystem refer to Caliptra Subsystem Hardware Specification Document.

Following high-level diagram helps integrators understand the overall architecture and the relationships between different components within the Caliptra subsystem.

Caliptra Subsystem includes:

- Caliptra Core: The Caliptra Core IP. For more information, see Caliptra: A Datacenter System on a Chip (SoC) Root of Trust (RoT).

- MCU (Manufacturer Control Unit): A microcontroller unit that manages various control tasks within the subsystem.

- I3C Core: An interface for connecting and communicating with I3C devices, which are used for providing streaming boot support and communicating with other I3C host controllers.

- Life Cycle Controller: A component that manages the different stages of the subsystem's lifecycle, including initialization, operation, and shutdown.

- Fuse Controller (OTP): A one-time programmable memory controller used for storing critical configuration data and security keys.

- MCI (Manufacturer Control Interface (for MCU)): Manages the communication between the processor and the memory components.

- Memories: Various memory components used for storing data and instructions required by the subsystem.

Integration Considerations

By performing these design and verification tasks, the integrator ensures that the Caliptra Subsystem is properly integrated and can function as intended within the larger system. Several files contain code that may be specific to an integrator's implementation and should be overridden. This overridable code is either configuration parameters with integrator-specific values or modules that implement process-specific functionality. Code in these files should be modified or replaced by integrators using components from the cell library of their fabrication vendor. The following table describes recommended modifications for each file.

| File | Description |

|---|---|

| css_mcu0_dmi_jtag_to_core_sync.v | Replace with a technology-specific sync cell. This synchronizer implements edge detection logic using a delayed flip flop on the output domain to produce a pulse output. Integrators must take care to ensure logical equivalence when replacing this logic with custom cells. |

| css_mcu0_beh_lib.sv | Replace css_mcu0_rvclkhdr/css_mcu0_rvoclkhdr with a technology-specific clock gater. Modifying this file may not be necessary if integrators override the clock gate module that is used by setting TECH_SPECIFIC_EC_RV_ICG. |

| css_mcu0_beh_lib.sv | Replace css_mcu0_rvsyncss (and css_mcu0_rvsyncss_fpga if the design will be implemented on an FPGA) with a technology-specific sync cell. |

| src/integration/rtl/caliptra_ss_includes.svh | Modify the parameter CPTRA_SS_ROM_SIZE_KB to define the correct size of the MCU ROM in integrated design. No other parameters in this file are permitted to be modified. |

Caliptra Core RTL modifications

It is mandatory that any build processes used (e.g. simulation, lint, synthesis) define the Verilog macro CALIPTRA_MODE_SUBSYSTEM, as described in the Caliptra Core Integration Specification. This ensures that Caliptra provides all Subsystem-related features and configuration. Example build scripts provided in the Caliptra Subsystem repository (such as Makefile) demonstrate how this might be performed.

Design Considerations

- Replace the AXI Interconnect: The subsystem utilizes an AXI-based interconnect to facilitate communication between components, with the Caliptra core connecting via an AXI interface. The integrator must replace the default AXI interconnect component with their proprietary interface. This ensures that the subsystem can communicate effectively with the rest of the subsystem components using the integrator's specific interconnect architecture.

- Connect the Memories: The integrator must connect the various memory components required by the subsystem. These memory components are used for storing data and instructions necessary for the operation of the Caliptra subsystem.

- No Changes to Internals: Integrators are not expected to make any changes to the internals of the design. The focus should be on ensuring proper integration and connectivity of the subsystem components.

Verification Considerations

- Connect the I3C Core GPIO with I3C host driver: The integrator must connect the I3C core (two target I3C devices) to the appropriate driver for the GPIO pins. This connection is crucial for enabling communication with I3C devices, which are used for communication within the subsystem.

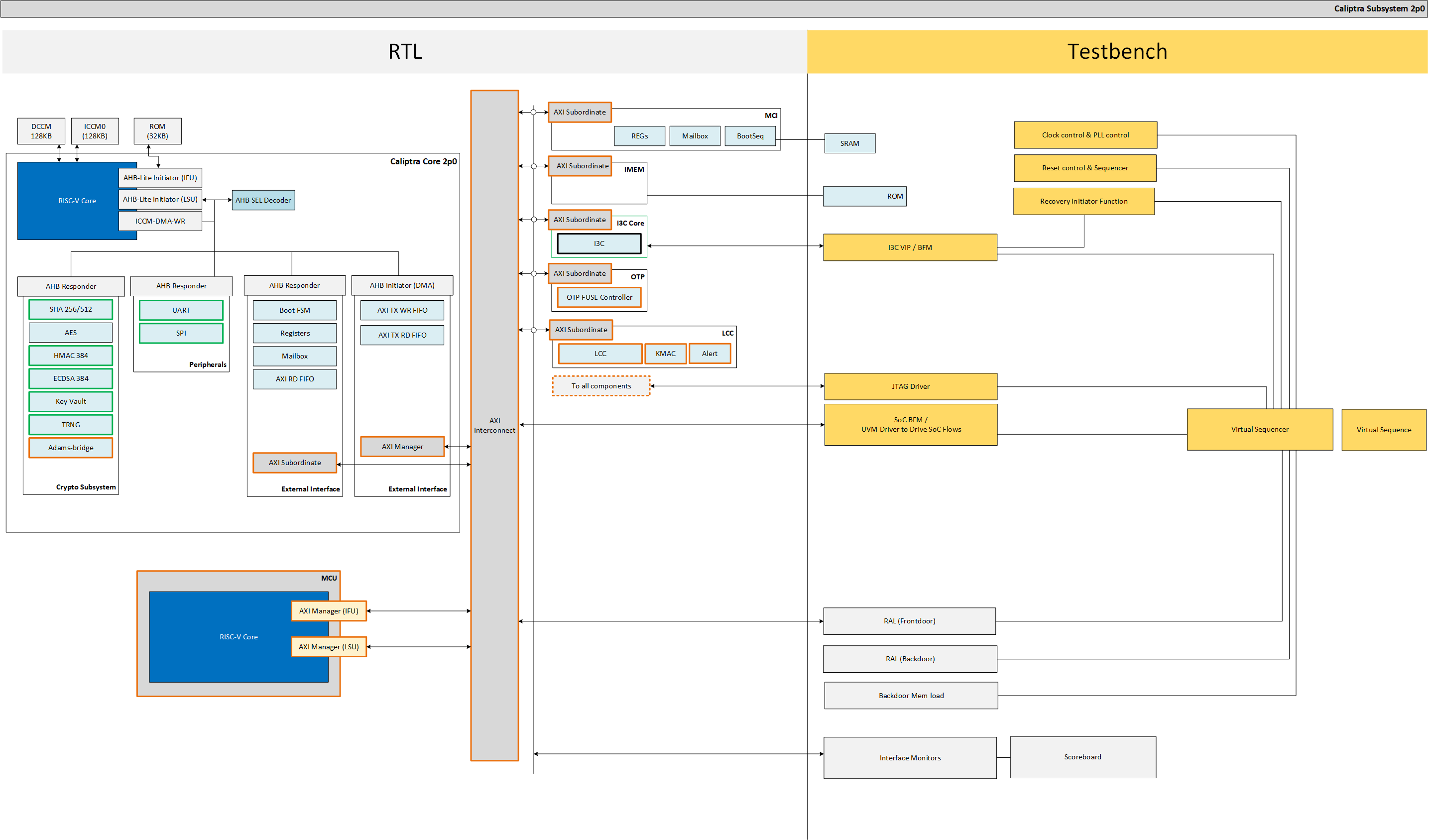

Verification View of Caliptra Subsystem

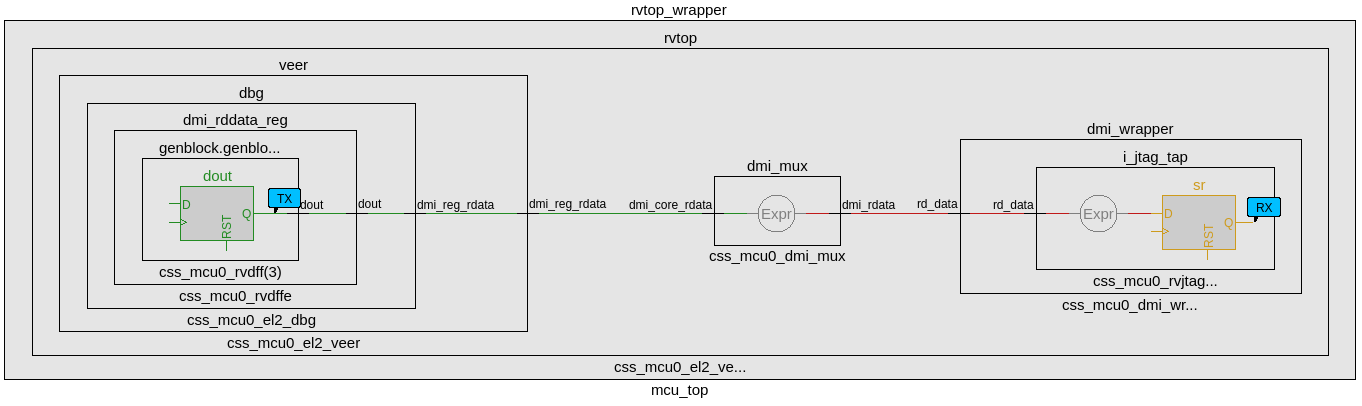

The following block diagram shows details on verification view of Caliptra Subsystem

Memory Requirements

Integrators must instantiate SRAM components outside of the Caliptra Subsystem boundary (see SRAM Implementation for more details). SRAM wrapper logic within the Caliptra Subsystem boundary facilitates the connection to SRAM instances through memory export interfaces in the top-level port list. Integrators must connect the following memory export interfaces to the instantiated SRAM components.

SoC Specific in below table means the size of the memory is not fixed and can be configured based on the design requirements by integrator. The actual size will depend on the specific implementation and configuration of the Caliptra Subsystem.

| Device | Memory Name | Interface | Size | Access Type | Description |

|---|---|---|---|---|---|

| MCU0 | Instruction ROM | mcu_rom_mem_export_if | SoC Specific | Read-Only | Stores the instructions for MCU0 execution. Write-enable (we) and write-data (wdata) signals must be left unconnected, as MCU ROM has no write support. |

| MCU0 | Memory Export | cptra_ss_mcu0_el2_mem_export | SoC Specific | Read/Write | Memory export for MCU0 access |

| MCU0 | Shared Memory (SRAM) | cptra_ss_mci_mcu_sram_req_if | SoC Specific | Read/Write | Shared memory between MCI and MCU for data storage |

| MAILBOX | MBOX0 Memory | cptra_ss_mci_mbox0_sram_req_if | SoC Specific | Read/Write | Memory for MBOX0 communication |

| MAILBOX | MBOX1 Memory | cptra_ss_mci_mbox1_sram_req_if | SoC Specific | Read/Write | Memory for MBOX1 communication |

| Caliptra Core | ICCM, DCCM | cptra_ss_cptra_core_el2_mem_export | Refer to Caliptra Core spec | Read/Write | Interface for the Instruction and Data Closely Coupled Memory (ICCM, DCCM) of the core |

| Caliptra Core | Caliptra ROM | cptra_ss_cptra_core_imem | Refer to Caliptra Core spec | Read-Only | Interface for Caliptra ROM |

| Caliptra Core | Caliptra Mailbox SRAM | cptra_ss_cptra_core_mbox_sram | Refer to Caliptra Core spec | Read/Write | Interface for Caliptra mailbox memory |

| Caliptra Core | Caliptra MLDSA SRAM | mldsa_memory_export_req | Refer to Caliptra Core spec | Read/Write | Interface for SRAM instantiated within Adams Bridge block |

Caliptra Subsystem Top

The integration of the Caliptra Subsystem begins with the instantiation of the top-level RTL module, caliptra_ss_top.sv. This module serves as the primary entry point for the subsystem and encapsulates all the logic and components required for the functionality of the Caliptra Root of Trust (RoT). All signals must be connected based on the detailed interface and signal descriptions provided in this document. Ensure adherence to the signal direction, width, and functionality to guarantee proper integration with the host SoC.

Parameters & Defines

File at this path in the repository includes parameters and defines for Caliptra Subsystem src/integration/rtl/caliptra_ss_includes.svh

Interfaces & Signals

IMPORTANT NOTE: All signals assumed to by synchronous to cptra_ss_clk_i.

Table: Caliptra SS Straps

| Facing | Type | width | Name | Description |

|---|---|---|---|---|

| External | input | 32 | cptra_ss_strap_mcu_lsu_axi_user_i | MCU LSU AXI user strap input |

| External | input | 32 | cptra_ss_strap_mcu_ifu_axi_user_i | MCU IFU AXI user strap input |

| External | input | 32 | cptra_ss_strap_mcu_sram_config_axi_user_i | MCU SRAM Configuration AXI user strap input. |

| External | input | 32 | cptra_ss_strap_mci_soc_config_axi_user_i | MCI SOC Configuration AXI user strap input |

| External | input | 32 | cptra_ss_strap_caliptra_dma_axi_user_i | Caliptra DMA AXI user strap input |

| External | input | 32 | cptra_ss_strap_mcu_reset_vector_i | MCU reset vector strap input |

| External | input | 64 | cptra_ss_strap_caliptra_base_addr_i | Caliptra base address strap input |

| External | input | 64 | cptra_ss_strap_mci_base_addr_i | MCI base address strap input |

| External | input | 64 | cptra_ss_strap_recovery_ifc_base_addr_i | Recovery interface base address strap input |

| External | input | 64 | cptra_ss_strap_otp_fc_base_addr_i | OTP FC base address strap input |

| External | input | 64 | cptra_ss_strap_uds_seed_base_addr_i | UDS seed base address strap input |

| External | input | 32 | cptra_ss_strap_prod_debug_unlock_auth_pk_hash_reg_bank_offset_i | Prod debug unlock auth PK hash reg bank offset input |

| External | input | 32 | cptra_ss_strap_num_of_prod_debug_unlock_auth_pk_hashes_i | Number of prod debug unlock auth PK hashes input |

| External | input | 32 | cptra_ss_strap_generic_0_i | Provides the Caliptra ROM with a 32-bit pointer that encodes the location of the fuse controller's status register and the bit position of the idle indicator. Upper 16 bits: Bit index of the IDLE_BIT_STATUS within SOC_OTP_CTRL_STATUS. Lower 16 bits: Offset address of SOC_OTP_CTRL_STATUS within the SOC_IFC_REG space, relative to SOC_OTP_CTRL_BASE_ADDR. |

| External | input | 32 | cptra_ss_strap_generic_1_i | Provides the Caliptra ROM with a 32-bit pointer to the fuse controller’s command register (CMD), enabling ROM-level control or triggering of fuse operations. |

| External | input | 32 | cptra_ss_strap_generic_2_i | Generic strap input 2 |

| External | input | 32 | cptra_ss_strap_generic_3_i | Generic strap input 3 |

| External | input | 1 | cptra_ss_debug_intent_i | Physical presence bit required to initiate the debug unlock flow. For more details, refer to the Production Debug Unlock Flow and How does Caliptra Subsystem enable manufacturing debug mode?. For SOCs that choose to use these features, this port should be connected to a GPIO |

AXI Interface (axi_if)

| Signal | Width | Direction (mgr) | Direction (sub) |

|---|---|---|---|

araddr | AW | output | input |

arburst | $bits(axi_burst_e) | output | input |

arsize | 3 | output | input |

arlen | 8 | output | input |

aruser | UW | output | input |

arid | IW | output | input |

arlock | 1 | output | input |

arvalid | 1 | output | input |

arready | 1 | input | output |

rdata | DW | input | output |

rresp | $bits(axi_resp_e) | input | output |

rid | IW | input | output |

rlast | 1 | input | output |

rvalid | 1 | input | output |

rready | 1 | output | input |

awaddr | AW | output | input |

awburst | $bits(axi_burst_e) | output | input |

awsize | 3 | output | input |

awlen | 8 | output | input |

awuser | UW | output | input |

awid | IW | output | input |

awlock | 1 | output | input |

awvalid | 1 | output | input |

awready | 1 | input | output |

wdata | DW | output | input |

wstrb | DW/8 | output | input |

wvalid | 1 | output | input |

wready | 1 | input | output |

wlast | 1 | output | input |

bresp | $bits(axi_resp_e) | input | output |

bid | IW | input | output |

bvalid | 1 | input | output |

bready | 1 | output | input |

Caliptra Subsystem Top Interface & Signals

| Facing | Type | width | Signal or Interface Name | Description |

|---|---|---|---|---|

| External | input | 1 | cptra_ss_clk_i | Caliptra subsystem clock input |

| External | input | 1 | cptra_ss_pwrgood_i | Power good signal input |

| External | input | 1 | cptra_ss_rst_b_i | Reset signal input, active low |

| External | input | 1 | cptra_ss_mci_cptra_rst_b_i | Reset signal input for Caliptra Core, active low. See Caliptra Core Reset Control for more details |

| External | output | 1 | cptra_ss_mci_cptra_rst_b_o | Reset signal output from MCI for Caliptra Core, active low. See Caliptra Core Reset Control for more details |

| External | input | 1 | cptra_ss_mcu_rst_b_i | Reset signal input for MCU, active low. See MCU Reset Control for more details |

| External | output | 1 | cptra_ss_mcu_rst_b_o | Reset signal output for MCU, active low. See MCU Reset Control for more details |

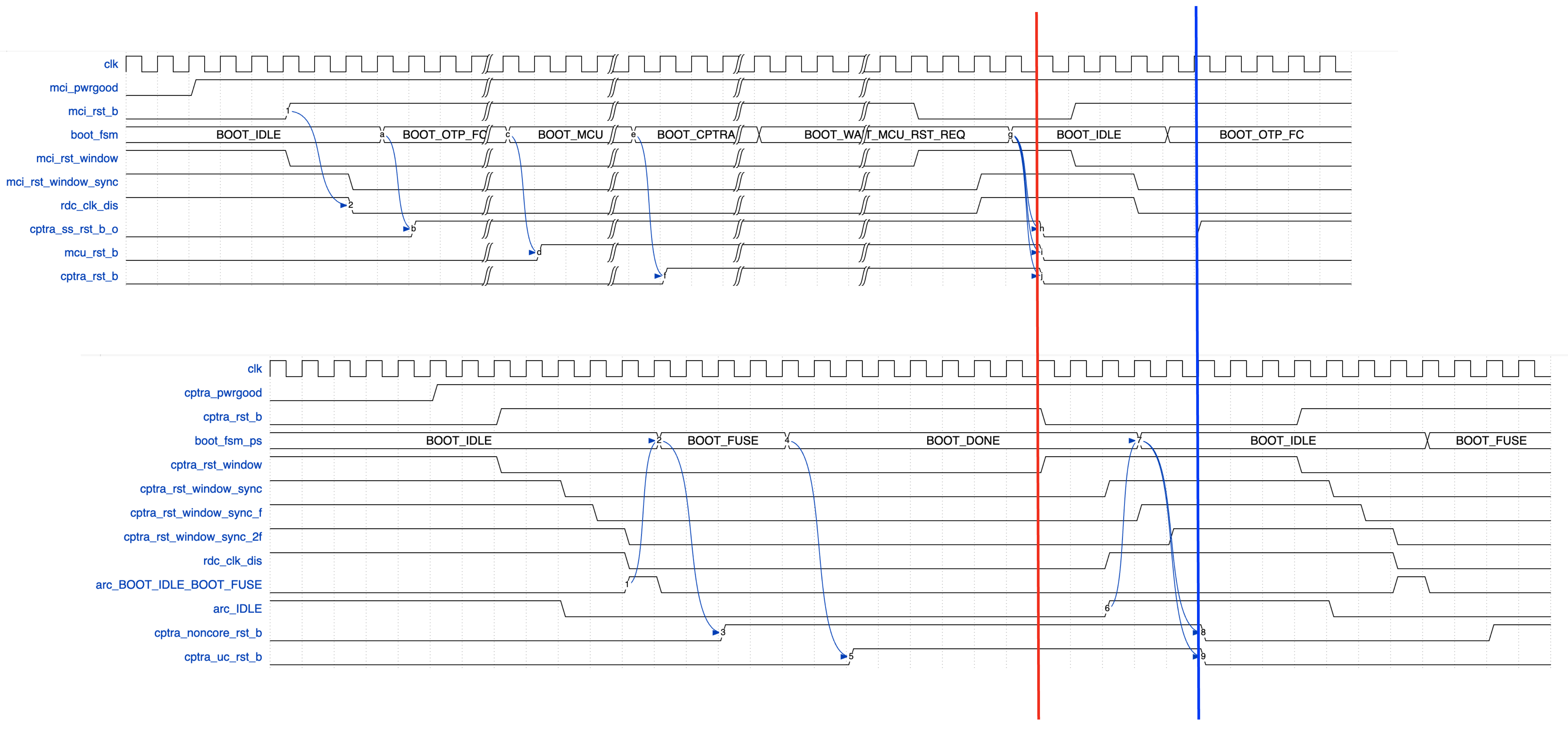

| External | output | 1 | cptra_ss_warm_reset_rdc_clk_dis_o | Clock disable for warm reset. Used to disable cptra_ss_rdc_clk_cg_o and cptra_ss_mcu_clk_cg_o clocks. Asserted a few clock cycles after cptra_ss_rst_b_i asserted and before cptra_ss_rst_b_o asserted. Deasserted a few clock cycles after cptra_ss_rst_b_i deasserted. |

| External | output | 1 | cptra_ss_early_warm_reset_warn_o | Early reset warn used to change security related signals to a safe value before reset is asserted. Needed since Caliptra Core clock gating is slightly after MCI clock gating/reset assertion. Example is the security_state fed from MCI to Caliptra Core. |

| External | output | 1 | cptra_ss_mcu_fw_update_rdc_clk_dis_o | Clock disable for MCU reset. Used to disable cptra_ss_mcu_clk_cg_o clock. Asserted a few clock cycles before cptra_ss_mcu_rst_b_o is asserted. Deasserted when MCI boot sequencer switches out of BOOT_RST_MCU state. |

| External | output | 1 | cptra_ss_rdc_clk_cg_o | Caliptra subsystem clock gated clock for RDC. Clock Control |

| External | output | 1 | cptra_ss_mcu_clk_cg_o | MCU clock gated clock for RDC. Clock Control |

| External | output | 1 | cptra_ss_rst_b_o | Caliptra subsystem reset aligned for RDC crossing Reset Control |

| External | axi_if | na | cptra_ss_cptra_core_s_axi_if_w_sub | Caliptra core AXI write sub-interface |

| External | axi_if | na | cptra_ss_cptra_core_s_axi_if_r_sub | Caliptra core AXI read sub-interface |

| External | axi_if | na | cptra_ss_cptra_core_m_axi_if_w_mgr | Caliptra core AXI write manager interface |

| External | axi_if | na | cptra_ss_cptra_core_m_axi_if_r_mgr | Caliptra core AXI read manager interface |

| External | axi_if | na | cptra_ss_mci_s_axi_if_w_sub | Caliptra Subsystem MCI AXI write sub-interface |

| External | axi_if | na | cptra_ss_mci_s_axi_if_r_sub | Caliptra Subsystem MCI AXI read sub-interface |

| External | axi_if | na | cptra_ss_mcu_rom_s_axi_if_w_sub | Caliptra Subsystem MCU ROM AXI write sub-interface. Writes to MCU ROM are not supported, this interface shall be left unconnected from AXI interconnect and tied to 0-value inputs. |

| External | axi_if | na | cptra_ss_mcu_rom_s_axi_if_r_sub | Caliptra Subsystem MCU ROM AXI read sub-interface |

| External | axi_if | na | cptra_ss_mcu_lsu_m_axi_if_w_mgr | Caliptra Subsystem MCU LSU AXI write manager interface |

| External | Output | 4 | cptra_ss_mcu_lsu_m_axi_if_awcache | Caliptra Subsystem MCU LSU AXI write manager address transaction attributes signal |

| External | Output | 3 | cptra_ss_mcu_lsu_m_axi_if_awprot | Caliptra Subsystem MCU LSU AXI write manager address protection type signal |

| External | Output | 4 | cptra_ss_mcu_lsu_m_axi_if_awregion | Caliptra Subsystem MCU LSU AXI write manager address region identifier signal |

| External | Output | 4 | cptra_ss_mcu_lsu_m_axi_if_awqos | Caliptra Subsystem MCU LSU AXI write manager address quality of service signal |

| External | axi_if | na | cptra_ss_mcu_lsu_m_axi_if_r_mgr | Caliptra Subsystem MCU LSU AXI read manager interface |

| External | Output | 4 | cptra_ss_mcu_lsu_m_axi_if_arcache | Caliptra Subsystem MCU LSU AXI read manager address transaction attributes signal |

| External | Output | 3 | cptra_ss_mcu_lsu_m_axi_if_arprot | Caliptra Subsystem MCU LSU AXI read manager address protection type signal |

| External | Output | 4 | cptra_ss_mcu_lsu_m_axi_if_arregion | Caliptra Subsystem MCU LSU AXI read manager address region identifier signal |

| External | Output | 4 | cptra_ss_mcu_lsu_m_axi_if_arqos | Caliptra Subsystem MCU LSU AXI read manager address quality of service signal |

| External | axi_if | na | cptra_ss_mcu_ifu_m_axi_if_w_mgr | Caliptra Subsystem MCU IFU AXI write manager interface |

| External | Output | 4 | cptra_ss_mcu_ifu_m_axi_if_awcache | Caliptra Subsystem MCU IFU AXI write manager address transaction attributes signal |

| External | Output | 3 | cptra_ss_mcu_ifu_m_axi_if_awprot | Caliptra Subsystem MCU IFU AXI write manager address protection type signal |

| External | Output | 4 | cptra_ss_mcu_ifu_m_axi_if_awregion | Caliptra Subsystem MCU IFU AXI write manager address region identifier signal |

| External | Output | 4 | cptra_ss_mcu_ifu_m_axi_if_awqos | Caliptra Subsystem MCU IFU AXI write manager address quality of service signal |

| External | axi_if | na | cptra_ss_mcu_ifu_m_axi_if_r_mgr | Caliptra Subsystem MCU IFU AXI read manager interface |

| External | Output | 4 | cptra_ss_mcu_ifu_m_axi_if_arcache | Caliptra Subsystem MCU IFU AXI read manager address transaction attributes signal |

| External | Output | 3 | cptra_ss_mcu_ifu_m_axi_if_arprot | Caliptra Subsystem MCU IFU AXI read manager address protection type signal |

| External | Output | 4 | cptra_ss_mcu_ifu_m_axi_if_arregion | Caliptra Subsystem MCU IFU AXI read manager address region identifier signal |

| External | Output | 4 | cptra_ss_mcu_ifu_m_axi_if_arqos | Caliptra Subsystem MCU IFU AXI read manager address quality of service signal |

| External | axi_if | na | cptra_ss_mcu_sb_m_axi_if_w_mgr | Caliptra Subsystem MCU System Bus AXI write manager interface |

| External | Output | 4 | cptra_ss_mcu_sb_m_axi_if_awcache | Caliptra Subsystem MCU System Bus AXI write manager address transaction attributes signal |

| External | Output | 3 | cptra_ss_mcu_sb_m_axi_if_awprot | Caliptra Subsystem MCU System Bus AXI write manager address protection type signal |

| External | Output | 4 | cptra_ss_mcu_sb_m_axi_if_awregion | Caliptra Subsystem MCU System Bus AXI write manager address region identifier signal |

| External | Output | 4 | cptra_ss_mcu_sb_m_axi_if_awqos | Caliptra Subsystem MCU System Bus AXI write manager address quality of service signal |

| External | axi_if | na | cptra_ss_mcu_sb_m_axi_if_r_mgr | Caliptra Subsystem MCU System Bus AXI read manager interface |

| External | Output | 4 | cptra_ss_mcu_sb_m_axi_if_arcache | Caliptra Subsystem MCU System Bus AXI read manager address transaction attributes signal |

| External | Output | 3 | cptra_ss_mcu_sb_m_axi_if_arprot | Caliptra Subsystem MCU System Bus AXI read manager address protection type signal |

| External | Output | 4 | cptra_ss_mcu_sb_m_axi_if_arregion | Caliptra Subsystem MCU System Bus AXI read manager address region identifier signal |

| External | Output | 4 | cptra_ss_mcu_sb_m_axi_if_arqos | Caliptra Subsystem MCU System Bus AXI read manager address quality of service signal |

| External | axi_if | na | cptra_ss_i3c_s_axi_if_w_sub | Caliptra Subsystem I3C AXI write sub-interface |

| External | axi_if | na | cptra_ss_i3c_s_axi_if_r_sub | Caliptra Subsystem I3C AXI read sub-interface |

| External | input | na | cptra_ss_lc_axi_wr_req_i | LC controller AXI write request input |

| External | output | na | cptra_ss_lc_axi_wr_rsp_o | LC controller AXI write response output |

| External | input | na | cptra_ss_lc_axi_rd_req_i | LC controller AXI read request input |

| External | output | na | cptra_ss_lc_axi_rd_rsp_o | LC controller AXI read response output |

| External | input | 128 | cptra_ss_raw_unlock_token_hashed_i | Hashed token for RAW unlock |

| External | input | na | cptra_ss_otp_core_axi_wr_req_i | OTP controller AXI write request input |

| External | output | na | cptra_ss_otp_core_axi_wr_rsp_o | OTP controller AXI write response output |

| External | input | na | cptra_ss_otp_core_axi_rd_req_i | OTP controller AXI read request input |

| External | output | na | cptra_ss_otp_core_axi_rd_rsp_o | OTP controller AXI read response output |

| External | input | 256 | cptra_ss_cptra_obf_key_i | Caliptra core obfuscation key input |

| External | input | CLP_CSR_HMAC_KEY_DWORDS | cptra_ss_cptra_csr_hmac_key_i | Caliptra core CSR HMAC key input |

| External | input | 1 | cptra_ss_cptra_core_jtag_tck_i | JTAG clock input |

| External | input | 1 | cptra_ss_cptra_core_jtag_tms_i | JTAG TMS input |

| External | input | 1 | cptra_ss_cptra_core_jtag_tdi_i | JTAG TDI input |

| External | input | 1 | cptra_ss_cptra_core_jtag_trst_n_i | JTAG reset input, active low |

| External | output | 1 | cptra_ss_cptra_core_jtag_tdo_o | JTAG TDO output |

| External | output | 1 | cptra_ss_cptra_core_jtag_tdoEn_o | JTAG TDO enable output |

| External | output | 125 | cptra_ss_cptra_generic_fw_exec_ctrl_o | Generic firmware execution control output |

| External | output | 1 | cptra_ss_cptra_generic_fw_exec_ctrl_2_mcu_o | Generic firmware execution control bit 2 from Caliptra output |

| External | input | 1 | cptra_ss_cptra_generic_fw_exec_ctrl_2_mcu_i | Generic firmware execution control bit 2 for MCU input |

| External | output | 1 | cptra_ss_all_error_fatal_o | Caliptra SS fatal error |

| External | output | 1 | cptra_ss_all_error_non_fatal_o | Caliptra SS non-fatal error |

| External | input | na | cptra_ss_lc_ctrl_jtag_i | LC controller JTAG request input |

| External | output | na | cptra_ss_lc_ctrl_jtag_o | LC controller JTAG response output |

| External | interface | na | cptra_ss_cptra_core_el2_mem_export | Caliptra core EL2 memory export interface |

| External | interface | na | mcu_rom_mem_export_if | MCU ROM memory export interface. Write-enable (we) and write-data (wdata) signals must be left unconnected, as MCU ROM has no write support. |

| External | output | 1 | cptra_ss_cptra_core_mbox_sram_cs_o | Mailbox SRAM chip select output |

| External | output | 1 | cptra_ss_cptra_core_mbox_sram_we_o | Mailbox SRAM write enable output |

| External | output | CPTRA_MBOX_ADDR_W | cptra_ss_cptra_core_mbox_sram_addr_o | Mailbox SRAM address output |

| External | output | CPTRA_MBOX_DATA_AND_ECC_W | cptra_ss_cptra_core_mbox_sram_wdata_o | Mailbox SRAM write data output |

| External | input | CPTRA_MBOX_DATA_AND_ECC_W | cptra_ss_cptra_core_mbox_sram_rdata_i | Mailbox SRAM read data input |

| External | output | 1 | cptra_ss_cptra_core_imem_cs_o | Instruction memory chip select output |

| External | output | CALIPTRA_IMEM_ADDR_WIDTH | cptra_ss_cptra_core_imem_addr_o | Instruction memory address output |

| External | input | CALIPTRA_IMEM_DATA_WIDTH | cptra_ss_cptra_core_imem_rdata_i | Instruction memory read data input |

| External | input | 1 | cptra_ss_cptra_core_bootfsm_bp_i | Boot FSM breakpoint input |

| External | output | 1 | cptra_ss_cptra_core_etrng_req_o | External TRNG request output |

| External | input | 4 | cptra_ss_cptra_core_itrng_data_i | Internal TRNG data input |

| External | input | 1 | cptra_ss_cptra_core_itrng_valid_i | Internal TRNG valid input |

| External | interface | na | cptra_ss_mci_mcu_sram_req_if | MCI MCU SRAM request interface |

| External | interface | na | cptra_ss_mci_mbox0_sram_req_if | MCI mailbox 0 SRAM request interface |

| External | interface | na | cptra_ss_mci_mbox1_sram_req_if | MCI mailbox 1 SRAM request interface |

| External | output | 1 | cptra_ss_soc_mcu_mbox0_data_avail | MCU Mailbox0 data available output |

| External | output | 1 | cptra_ss_soc_mcu_mbox1_data_avail | MCU Mailbox1 data available output |

| External | interface | na | cptra_ss_mcu0_el2_mem_export | MCU0 EL2 memory export interface |

| External | input | 64 | cptra_ss_mci_generic_input_wires_i | Generic input wires for MCI |

| External | input | 1 | cptra_ss_mcu_no_rom_config_i | No ROM configuration input |

| External | input | 1 | cptra_ss_mci_boot_seq_brkpoint_i | MCI boot sequence breakpoint input |

| External | input | 1 | cptra_ss_lc_Allow_RMA_or_SCRAP_on_PPD_i | Allow RMA or SCRAP on PPD input |

| External | input | 1 | cptra_ss_FIPS_ZEROIZATION_PPD_i | Zeroization request with PPD input. If FIPS zeroization flow is required, it shall be set before Caliptra SS is out of reset. |

| External | output | 1 | cptra_ss_dbg_manuf_enable_o | Indication that the debug is unlocked for manufacturing state and this is set by Caliptra Core |

| External | output | 64 | cptra_ss_cptra_core_soc_prod_dbg_unlock_level_o | Indication that the debug is unlocked for production state. Each bit represents a debug level. Currently, 8-bit is supported with Caliptra ROM |

| External | output | na | caliptra_ss_life_cycle_steady_state_o | Life-cycle state broadcasted by fuse macro for any additional SOC specific use cases |

| External | output | 1 | caliptra_ss_otp_state_valid_o | One-bit valid indicator for the broadcast life-cycle state (caliptra_ss_life_cycle_steady_state_o). |

| External | output | 1 | caliptra_ss_volatile_raw_unlock_success_o | Asserted when the life-cycle controller grants the volatile-unlock state and remains asserted until the next power-cycle. This transition bypasses the fuse macro, so caliptra_ss_life_cycle_steady_state_o and caliptra_ss_otp_state_valid_o do not reflect it. |

| External | output | 64 | cptra_ss_mci_generic_output_wires_o | Generic output wires for MCI |

| External | input | 1 | cptra_ss_mcu_jtag_tck_i | MCU JTAG clock input |

| External | input | 1 | cptra_ss_mcu_jtag_tms_i | MCU JTAG TMS input |

| External | input | 1 | cptra_ss_mcu_jtag_tdi_i | MCU JTAG TDI input |

| External | input | 1 | cptra_ss_mcu_jtag_trst_n_i | MCU JTAG reset input, active low |

| External | output | 1 | cptra_ss_mcu_jtag_tdo_o | MCU JTAG TDO output |

| External | output | 1 | cptra_ss_mcu_jtag_tdoEn_o | MCU JTAG TDO enable output |

| External | input | 1 | cptra_ss_i3c_scl_i | I3C clock input |

| External | input | 1 | cptra_ss_i3c_sda_i | I3C data input |

| External | output | 1 | cptra_ss_i3c_scl_o | I3C clock output |

| External | output | 1 | cptra_ss_i3c_sda_o | I3C data output |

| External | output | 1 | cptra_ss_i3c_scl_oe | I3C clock output enable |

| External | output | 1 | cptra_ss_i3c_sda_oe | I3C data output enable |

| External | input | 1 | cptra_i3c_axi_user_id_filtering_enable_i | I3C AXI user filtering enable (active high) |

| External | output | 1 | cptra_ss_sel_od_pp_o | Select open-drain push-pull output |

| External | output | 1 | cptra_ss_i3c_recovery_payload_available_o | I3C indicates recovery payload is available. If there is no external I3C it should be looped back to cptra_ss_i3c_recovery_payload_available_i. If there is an external I3C it can be combined with or replaced with SOC logic and connected to cptra_ss_i3c_recovery_payload_available_i |

| External | input | 1 | cptra_ss_i3c_recovery_payload_available_i | I3C indication for Caliptra Core that a recovery payload is available. If no external I3C should be connected to cptra_ss_i3c_recovery_payload_available_o. If external I3C it can be connected to a combination of SOC logic + cptra_ss_i3c_recovery_payload_available_o |

| External | output | 1 | cptra_ss_i3c_recovery_image_activated_o | Indicates the recovery image is activated. If there is no external I3C it should be looped back to cptra_ss_i3c_recovery_image_activated_i. If there is an external I3C it can be combined with or replaced with SOC logic and connected to cptra_ss_i3c_recovery_image_activated_i |

| External | input | 1 | cptra_ss_i3c_recovery_image_activated_i | I3C indication for Caliptra Core that the recovery image is activated. If no external I3C should be connected to cptra_ss_i3c_recovery_image_activated_o. If there is an external I3C it can be connected to a combination of SOC logic + cptra_ss_i3c_recovery_image_activated_o |

| External | input | 64 | cptra_ss_cptra_core_generic_input_wires_i | Generic input wires for Caliptra core |

| External | input | 1 | cptra_ss_cptra_core_scan_mode_i | Caliptra core scan mode input |

| External | output | 1 | cptra_error_fatal | Fatal error output |

| External | output | 1 | cptra_error_non_fatal | Non-fatal error output |

| External | output | 1 | cptra_ss_mcu_halt_status_o | MCU halt status |

| External | output | 1 | cptra_ss_mcu_halt_status_i | MCU halt status input used by MCI |

| External | output | 1 | cptra_ss_mcu_halt_ack_o | MCU halt ack |

| External | output | 1 | cptra_ss_mcu_halt_ack_i | MCU halt ack input used by MCI |

| External | output | 1 | cptra_ss_mcu_halt_req_o | MCU halt request |

Integration Requirements

Clock

The cptra_ss_clk_i signal is the primary clock input for the Caliptra Subsystem.

- Signal Name

cptra_ss_clk_i - Required Frequency 333* MHz to 400 MHz

- I3C core imposes requirement for minimum operating clock frequency set to 333 MHz or higher to meet 12ns tSCO timing.

- SoCs that run Caliptra lower than 333 MHz will limit the max I3C SCL frequency. See I3C Phy Spec for more details.

- This was changed from 170 MHz floor due to CDC issue found in I3C core:

- Clock Source Must be derived from the SoC’s clock generation module or a stable external oscillator.

- Integration Notes

- Verify that the SoC or system-level clock source provides a stable clock.

- The clock signal must be properly buffered if necessary to meet the subsystem's setup and hold timing requirements.

- If a different frequency is required, ensure that a clock divider or PLL is used to generate clock before connection.

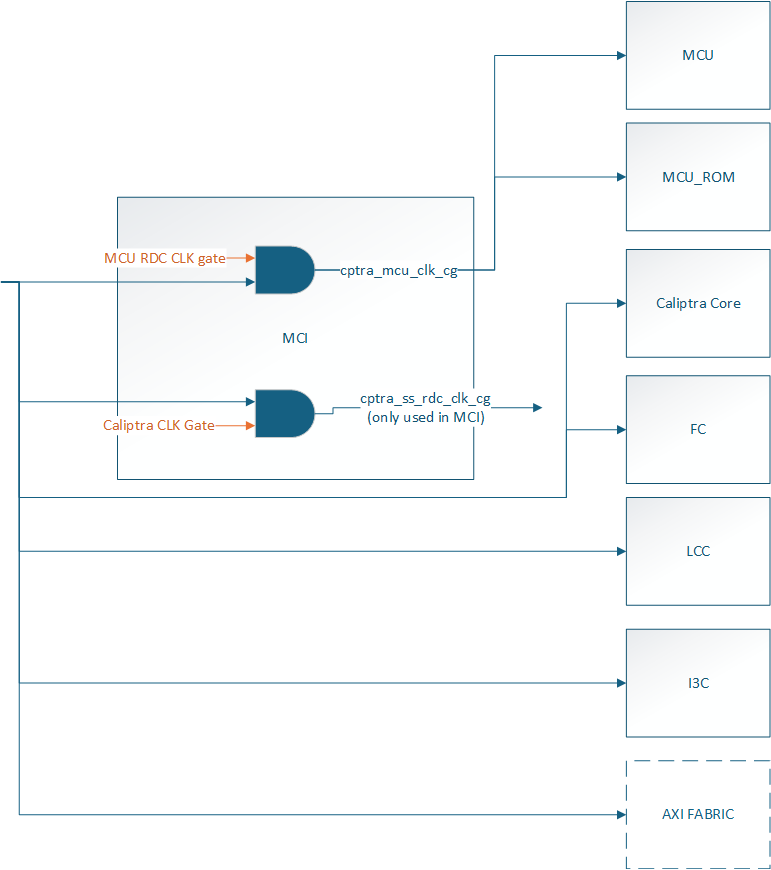

The cptra_ss_rdc_clk_cg_o output clock is a clock gated version of cptra_ss_clk_i. It is clock gated whenever cptra_ss_rst_b is asserted to avoid RDC issues from the warm reset domain to the cold reset domain/memories.

- Signal Name

cptra_ss_rdc_clk_cg_o - Required Frequency Same as

cptra_ss_clk_i. - Clock Source Caliptra SS MCI clock gater

- Integration Notes

- Gated a few clock cycles before

cptra_ss_rst_b_oasserted and remains gated until reset is deasserted. - MCU SRAM and MCU MBOX memories shall be connected to this clock to avoid RDC issues.

- Clock gating controlled by

cptra_ss_warm_reset_rdc_clk_dis_o. - Any SOC logic on a deeper reset domain than CSS can use this clock to resolve RDC issues.

- Gated a few clock cycles before

The cptra_ss_mcu_clk_cg_o output clock is a gated version of cptra_ss_clk_i. It is gated whenever cptra_ss_mcu_rst_b_o is asserted to avoid RDC issues within the MCU warm and cold reset domains.

- Signal Name

cptra_ss_mcu_clk_cg_o - Required Frequency Same as

cptra_ss_clk_i. - Clock Source Caliptra SS MCI clock gater

- Integration Notes

- Gated a few clock cycles before

cptra_ss_mcu_rst_b_oasserted and remains gated until reset is deasserted. - Clock gating controlled by

cptra_ss_mcu_fw_update_rdc_clk_dis_oandcptra_ss_warm_reset_rdc_clk_dis_o. - Any SOC logic on a deeper reset domain than MCU can use this clock to resolve RDC issues.

- Gated a few clock cycles before

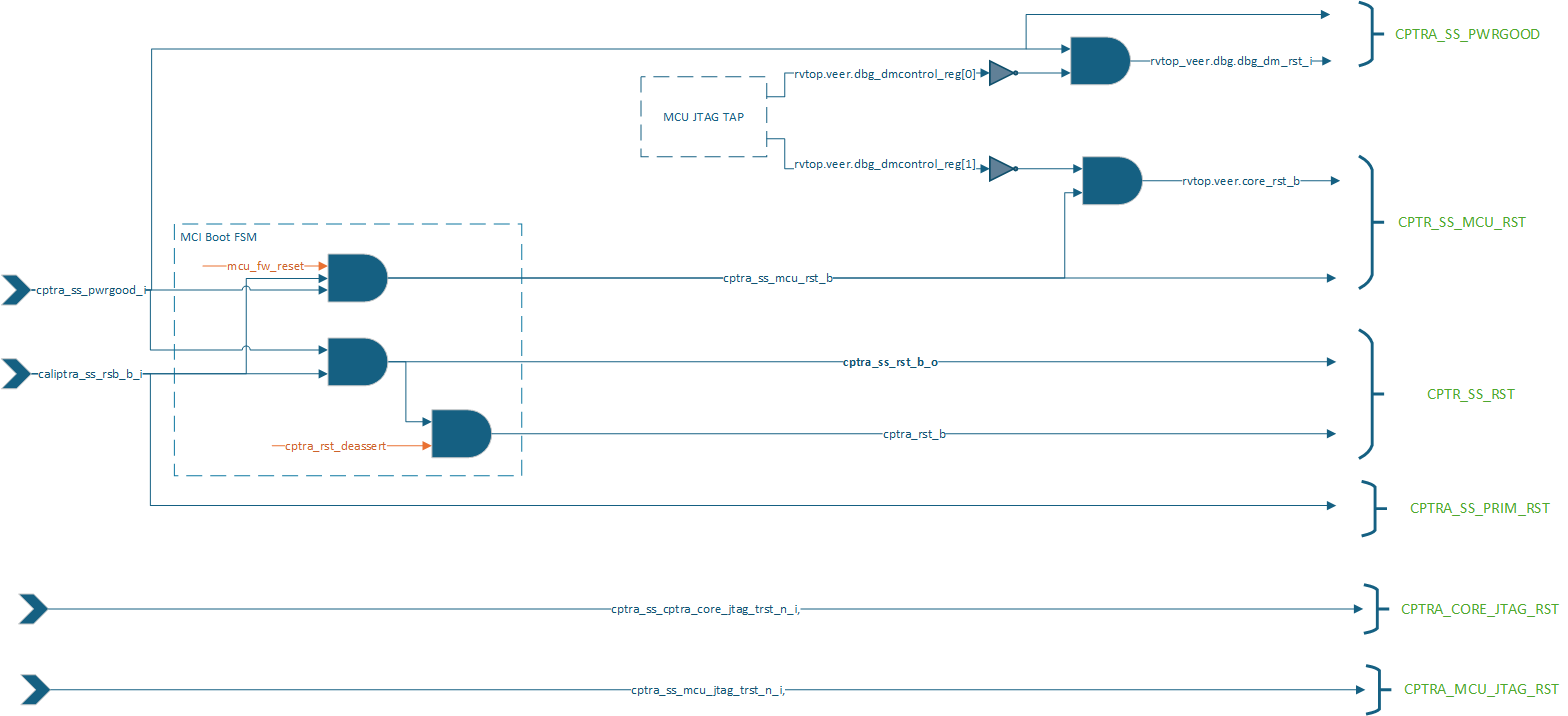

Reset

The cptra_ss_rst_b_i signal is the primary reset input for the Caliptra Subsystem. It must be asserted low to reset the subsystem and de-asserted high to release it from reset. Ensure that the reset is held low for a sufficient duration (minimum of 2 clock cycles) to allow all internal logic to initialize properly.

- Signal Name

cptra_ss_rst_b_i - Active Level Active-low (

0resets the subsystem,1releases reset) - Reset Type Synchronous with the

cptra_ss_clk_isignal - Integration Notes

- The reset signal must be synchronized to the

cptra_ss_clk_iclock to prevent metastability issues. - If the reset source is asynchronous, a synchronizer circuit must be used before connecting to the subsystem.

- During SoC initialization, assert this reset signal until all subsystem clocks and required power domains are stable.

- It is illegal to only toggle

cptra_ss_rst_b_iuntil both Caliptra and MCU have received at least one FW update. Failure to follow this requirement could cause them to execute out of an uninitialized SRAM. - SOC should assert

cptra_ss_reset_b_iaftercptra_ss_mcu_halt_status_ois asserted to guarantee MCU is idle. This will guarantee no outstanding AXI transactions from MCU and help avoid RDC issues.

- The reset signal must be synchronized to the

The cptra_ss_rst_b_o is a delayed version of cptra_ss_rst_b_i to ensure cptra_ss_rdc_clk_cg_o is gated before reset is asserted. This reset is needed for the purpose of RDC between the warm reset domain and the cold reset/memory domain.

- Signal Name

cptra_ss_rst_b_o - Active Level Active-low (

0resets the subsystem,1releases reset) - Reset Type Synchronous with the

cptra_ss_rdc_clk_cg_osignal - Integration Notes

- SOCs shall use this reset for any memory logic connected to MCU SRAM or MCU MBOX to avoid RDC corruption of the memories.

- It is recommended to be used for SOC AXI interconnect if it is on the same reset domain as Caliptra SS to avoid RDC issues.

- SOC logic on

cptra_ss_rst_b_idomain and transitions into a deeper reset domain can use this reset paired withcptra_ss_rdc_clk_cg_oto avoid RDC issues.

Power Good Signal

The cptra_ss_pwrgood_i signal serves as an indicator of stable power for the Caliptra Subsystem. When asserted (1), it confirms that power is stable and the subsystem can operate normally. When deasserted (0), the signal triggers a hard reset of the subsystem. Deassertion must be synchronized to cptra_ss_clk_i to avoid metastability issues.

- Signal Name

cptra_ss_pwrgood_i - Active Level Active-high (

1indicates stable power,0triggers reset) - Assertion Type Asynchronous

- Deassertion Type Synchronous to

cptra_ss_clk_i - Integration Notes

- Ensure

cptra_ss_pwrgood_iis properly generated by the power management unit or system power controller. - Since assertion is asynchronous, it must be immediately driven high once power is stable.

- Use a synchronizer to properly align deassertion with

cptra_ss_clk_ito prevent glitches. - If

cptra_ss_pwrgood_iremains low, the Caliptra Subsystem will remain in a hard reset state.

- Ensure

Connecting AXI Interconnect

Integrator must connect following list of manager and subordinates to axi interconnect.

- List of AXI Manager connections to AXI interconnect.

| Manager AXI If Name | Description |

|---|---|

cptra_ss_mcu_lsu_m_axi_if | Manager interface for MCU Load/Store Unit (LSU). All additional AXI signals present in the top-level port list that are not part of the axi_if interface must also be connected to the AXI interconnect (AxCACHE, AxPROT, AxREGION, AxQOS). |

cptra_ss_mcu_ifu_m_axi_if | Manager interface for MCU Instruction Fetch Unit (IFU). All additional AXI signals present in the top-level port list that are not part of the axi_if interface must also be connected to the AXI interconnect (AxCACHE, AxPROT, AxREGION, AxQOS). |

cptra_ss_mcu_sb_m_axi_if | Manager interface for MCU System Bus (SB). Used for debug only. All additional AXI signals present in the top-level port list that are not part of the axi_if interface must also be connected to the AXI interconnect (AxCACHE, AxPROT, AxREGION, AxQOS). |

cptra_ss_cptra_core_m_axi_if | Manager interface for the Caliptra Core AXI transactions. Additional signals are unused and may be tied to 0 at the interconnect (AxCACHE, AxPROT, AxREGION, AxQOS). |

-

AXI USER width is 32-bits for all AXI interfaces in the Caliptra Subsystem. Only the Address User signals are used (ARUSER and AWUSER) for secure access filtering. Other USER signals are either tied to 0 or not used (WUSER, RUSER, BUSER). ARUSER and AWUSER must be passed unmodified through the AXI interconnect to all AXI subordinates in the Subsystem. Each logic block inside the Subsystem is responsible for performing its own AXI User filtering based on access privileges. AXI interconnect is only responsible for passing the unmodified signals along with the transaction requests, not for performing any access filtering.

-

AXI ID width at each MCU manager interface must not be modified from the configured values. ID width for each of the MCU AXI Manager interfaces is defined by the <IF_NAME>_BUS_TAG parameter from this file: css_mcu0_el2_param.vh. Port connections may be seen in mcu_top.sv. ID Width of the Caliptra DMA AXI Manager interface is defined in soc_ifc_pkg.sv.

- IFU_BUS_TAG: 3. Interconnect should support ID values 0-7.

- LSU_BUS_TAG: 3. Interconnect should support ID values 0-7.

- SB_BUS_TAG: 1. Interconnect should support ID values 0,1.

- CPTRA_AXI_DMA_ID_WIDTH: 5. ID signals are tied to constant 0.

-

For each AXI subordinate interface in the Subsystem the following table shows ID WIDTH default value, file to review for the configured definition, and any support for configurability. | Interface | Default ID WIDTH | Reference File | Description | | ----------- | ------------------ | ---------------------------------- | ---------------------------------------------------------------- | | cptra_ss_cptra_core_s_axi_if | 8 | config_defines.svh | Default value of 8 is controlled using the macro

CALIPTRA_AXI_ID_WIDTH. | | cptra_ss_mcu_rom_s_axi_if | 8 | config_defines.svh | Default value of 8 is controlled using the macroCALIPTRA_AXI_ID_WIDTH. | | cptra_ss_mci_s_axi_if | 8 | caliptra_ss_top.sv | ID_WIDTH value is derived from the width of AxID signals in the connected AXI interface. | | cptra_ss_i3c_s_axi_if | 8 | i3c_defines.svh | Default value of 8 is controlled using the macroAXI_ID_WIDTH. | | cptra_ss_lc_axi_wr, cptra_ss_lc_axi_rd | 8 | src/tlul/rtl/tlul_pkg.sv | Default value is derived from the macroCALIPTRA_AXI_ID_WIDTH, overrideable using the macroCALIPTRA_SS_TLUL_AXI_ID_WIDTH. | | cptra_ss_otp_core_axi_wr, cptra_ss_otp_core_axi_rd | 8 | src/tlul/rtl/tlul_pkg.sv | Default value is derived from the macroCALIPTRA_AXI_ID_WIDTH, overrideable using the macroCALIPTRA_SS_TLUL_AXI_ID_WIDTH. | -

AXI subordinates in the Subsystem may accept up to 2 Read and 2 Write requests in total, but each request is serviced in order and responses are provided in order. Integrators may configure the interconnect to issue 1 or 2 outstanding transactions, but are recommended to configure only a single outstanding request at a time for area (buffer) optimizations in the interconnect and because there is no significant performance improvement by queueing multiple requests.

-

Subordinate Address Map requirements

- The MCU is configured with several internal address assignments that must not be used when assigning SOC addresses for AXI subordinates on the AXI interconnect. The following table shows these restricted regions:

| Start Address | End Address | Name | Description |

|---|---|---|---|

| 64'h5000_0000 | 64'h5FFF_FFFF | MCU DCCM | MCU Data Closely Coupled Memory. No external subordinates may be assigned address space in the same 256MiB region as the DCCM. For more details, refer to the VeeR EL2 Programmer's Reference Manual. |

| 64'h6000_0000 | 64'h6FFF_FFFF | MCU PIC | MCU Programmable Interrupt Controller. No external subordinates may be assigned address space in the same 256MiB region as the PIC. For more details, refer to the VeeR EL2 Programmer's Reference Manual. |

-

Subordinate Address Map (reference only) / List of sub connected to Interconnect

- The following address map is a suggested address map for subordinates for the subsystem design. It details the memory layout and the connections between different components within the Caliptra subsystem.

| Start Address | End Address | Address Width | Subordinate | Name | Description |

|---|---|---|---|---|---|

| 64'h1000_0000 | 64'h1FFF_FFFF | - | 0 | n/a | Reserved |

| 64'h2000_4000 | 64'h2000_4FFF | 12 | 1 | I3c | I3C Core |

| 64'h8000_0000 | 64'h80FF_FFFF | 24 | 2 | MCU ROM | MCU ROM |

| 64'hA002_0000 | 64'hA003_FFFF | 17 | 3 | SoC IFC | Caliptra Core AXI subordinate interface |

| 64'h2100_0000 | 64'h21DF_FFFF | 24 | 4 | MCI | Manufacturer Control Interface (for MCU) |

| 64'h7000_0000 | 64'h7000_01FF | 9 | 5 | Fuse Ctrl | Fuse Controller |

| 64'h7000_0400 | 64'h7000_05FF | 9 | 6 | Life Cycle Ctrl | Life Cycle Controller |

-

Following are the header files path for the below suggested address map. These files would be useful in defining the address map using the given RDL Files.

Caliptra Subsystem Reference Register Map

Caliptra Subsystem Reference Register Map. Please note, any addresses are for the example purpose only.

FW Execution Control Connections

FW Execute Control is typically controlled by Caliptra. This means cptra_ss_cptra_generic_fw_exec_ctrl_2_mcu_o should be looped back and directly connected to cptra_ss_cptra_generic_fw_exec_ctrl_2_mcu_i. If the SOC decided to not use Caliptra Core, the SOC must drive cptra_ss_cptra_generic_fw_exec_ctrl_2_mcu_i the same way Caliptra Core drives this signal.

- On same reset at MCI

- Synchronous to MCI clock domain

- 1 indicates FW patch is valid in the MCU SRAM

- 0 indicates FW patch is invalid and will request MCU to reset itself See Hitless Update Flow to understand exactly when this signal shall be set/cleared in the hitless FW flow.

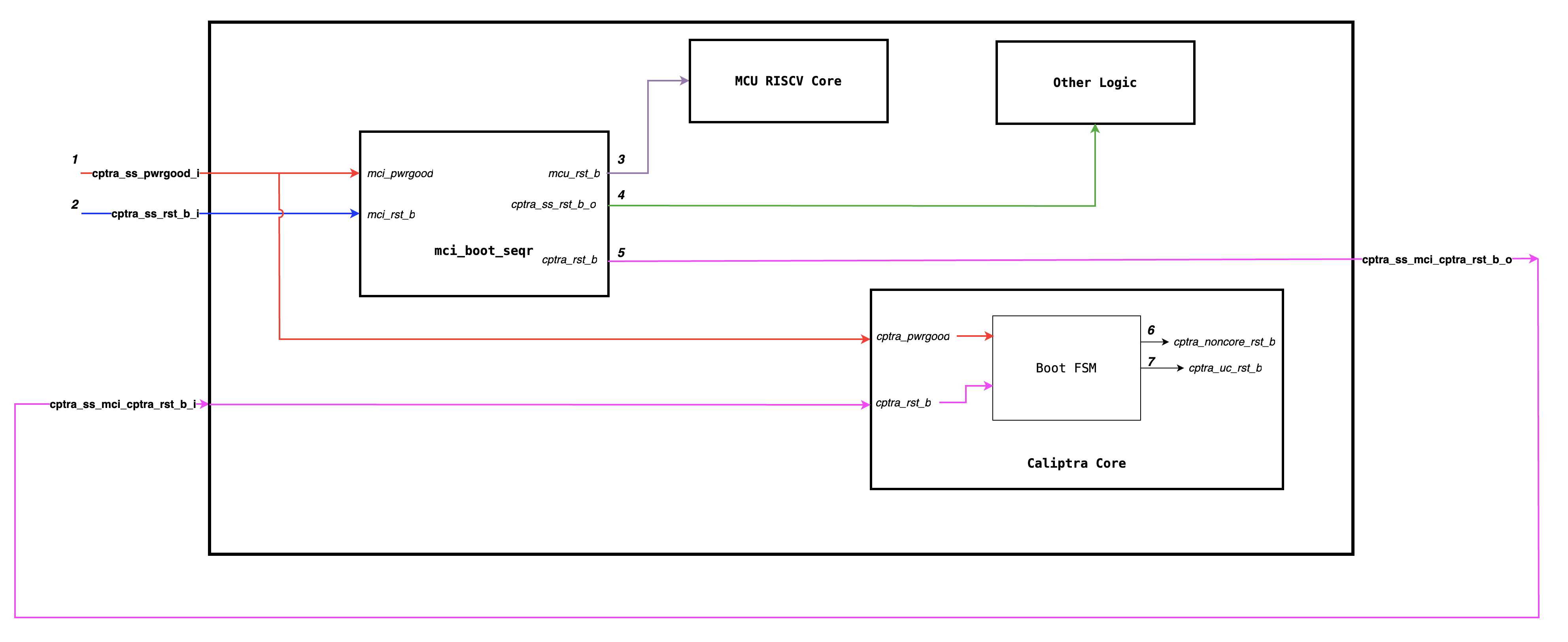

Caliptra Core Reset Control

Typically Caliptra reset is directly controlled by MCI. This means cptra_ss_mci_cptra_rst_b_o is directly looped back to cptra_ss_mci_cptra_rst_b_i.

If an SOC wants to keep Caliptra in reset they can tie off cptra_ss_mci_cptra_rst_b_i and not user cptra_ss_mci_cptra_rst_b_o.

If an SOC wants to modify Caliptra reset they can do so by adding additional logic to the above signals.

NOTE: Caliptra SS RDC and CDC are only evaluated when the MCI control is looped back to Caliptra. Any modification to this reset control requires a full RDC and CDC analysis done by the SOC integration team.

MCU Reset Control

Typically MCU reset is directly controlled by MCI. This means cptra_ss_mcu_rst_b_o is directly looped back to cptra_ss_mcu_rst_b_i.

The SOC can choose to delay the MCU reset deassertion. The SOC should be aware that MCU clock enable is based off cptra_ss_mcu_rst_b_o.

If the SOC wants to delay assertion of MCU reset this can be done, but integrators need to be aware the MCU reset counter (MIN_MCU_RST_COUNTER_WIDTH) starts counting when cptra_ss_mcu_rst_b_i asserts. Meaning MCU could be in reset for shorter than expected. To resolve this issue the SOC should implement their own reset counter to delay the reset deassertion.

Arbitrary reset assertions/deassertions should not be done unless the integrator understands exactly what they are doing. This can cause RDC issues within Caliptra SS.

NOTE: Caliptra SS RDC and CDC are only evaluated when MCU reset is looped back. Any modification to this reset control requires a full RDC and CDC analysis done by the SOC integration team.

SRAM implementation

Overview

SRAMs are instantiated at the SoC level. Caliptra Subsystem provides the interface to export SRAMs from internal components. Components that export SRAMs include:

- Caliptra Core (see Caliptra Core integration specification)

- MCU (RISC-V core)

- MCI (Mailbox SRAM and MCU SRAM)

SRAM repair logic (for example, BIST) and its associated fuses, which is proprietary to companies and their methodologies, is implemented external to the Caliptra Subsystem boundary.

SRAMs must NOT go through BIST or repair flows across a “warm reset”. SoC shall perform SRAM repair during a powergood cycling event ("cold reset") and only prior to deasserting cptra_ss_rst_b_i. During powergood cycling events, SoC shall also initialize all entries in the SRAM to a 0 value prior to deasserting cptra_ss_rst_b_i. This requirement can not be completed by MCU (or any other components in Subsystem) because it is a function of the proprietary SRAM management logic.

MCU mailbox and executable SRAMs are implemented with ECC protection. Data width for the mailbox is 32-bits, with 7 parity bits for a Hamming-based SECDED (single-bit error correction and double-bit error detection).

RISC-V internal memory export

To support synthesis flexibility and ease memory integration to various fabrication processes, all SRAM blocks inside the RISC-V cores (Caliptra Core and MCU) are exported to an external location in the testbench. A single unified interface connects these memory blocks to their parent logic within the RISC-V core. Any memory implementation may be used to provide SRAM functionality in the external location in the testbench, provided the implementation adheres to the interface requirements connected to control logic inside the processor. Memories behind the interface are expected to be implemented as multiple banks of SRAM, from which the RISC-V processor selects the target using an enable vector. The I-Cache has multiple ways, each containing multiple banks of memory, and SOC SRAM implementations for I-Cache must be compatible with the exported interface.

The following memories are exported:

- Instruction Closely-Coupled Memory (ICCM) (Caliptra Core only)

- Data Closely Coupled Memory (DCCM) (Caliptra Core and MCU)

- Instruction Cache (I-Cache) (MCU only)

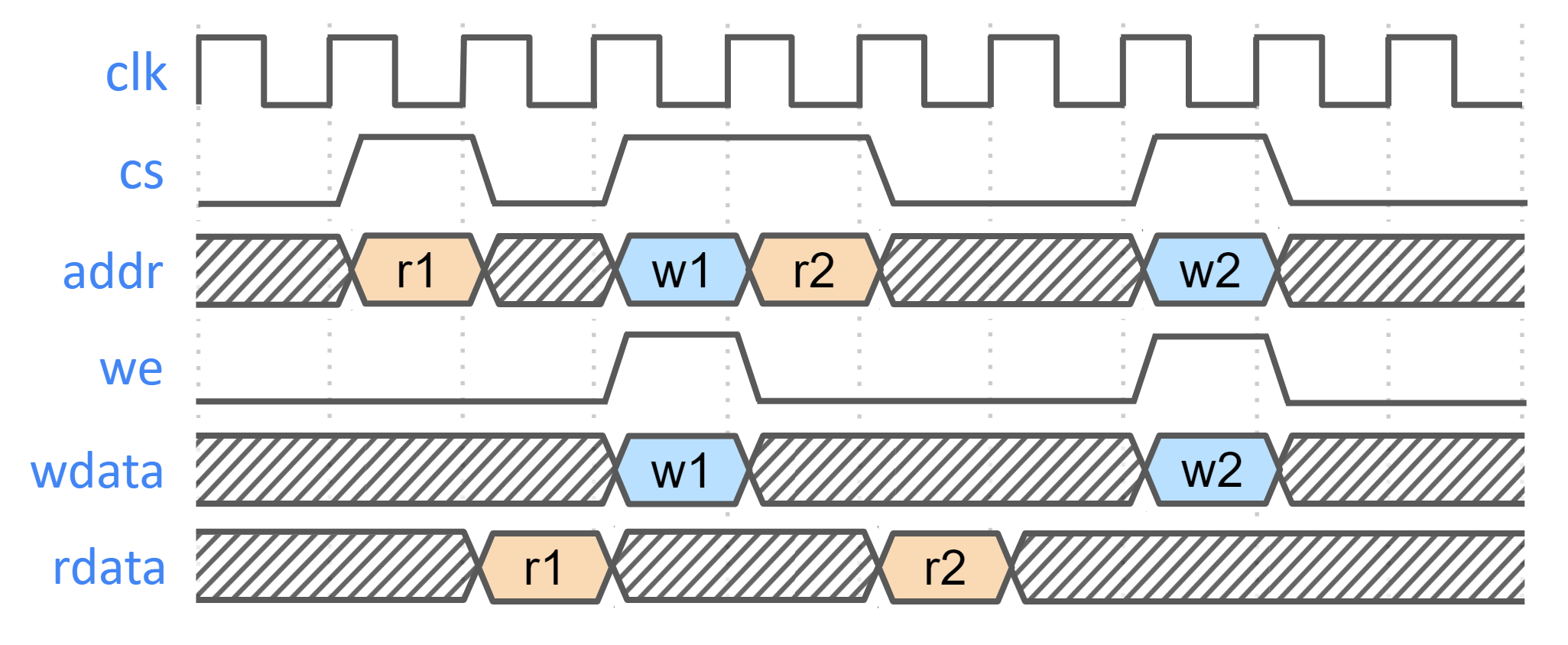

SRAM timing behavior

- [Writes] SRAM input wren signal is asserted simultaneously with input data and address. Input data is stored at the input address 1 clock cycle later.

- [Reads] SRAM input clock enable signal is asserted simultaneously with input address. Output data is available 1 clock cycle later from a flip-flop register stage.

The following figure shows the SRAM interface timing.

Figure: SRAM interface timing

SRAM parameterization

Parameterization for ICCM/DCCM/I-Cache memories is derived from the configuration of the VeeR RISC-V core that has been selected for Caliptra Subsystem integration. Parameters defined in the VeeR core determine signal dimensions at the Subsystem top-level interface and drive requirements for SRAM layout. For details about interface parameterization, see the Interfaces & Signals section.

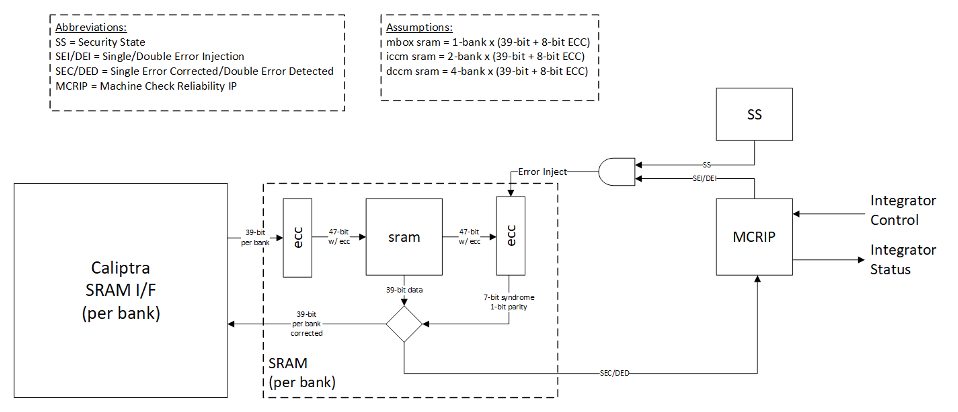

Example SRAM machine check reliability integration

This section describes an example implementation of integrator machine check reliability.

This example is applicable to scenarios where an integrator may need control of or visibility into SRAM errors for purposes of reliability or functional safety. In such cases, integrators may introduce additional layers of error injection, detection, and correction logic surrounding SRAMs. The addition of such logic is transparent to the correct function of Caliptra Subsystem, and removes integrator dependency on Caliptra Subsystem components for error logging or injection.

Note that the example assumes that data and ECC codes are in non-deterministic bit-position in the exposed SRAM interface bus. Accordingly, redundant correction coding is shown in the integrator level logic (i.e., integrator_ecc(caliptra_data, caliptra_ecc)). If the Caliptra Subsystem data and ECC are deterministically separable at the Caliptra Subsystem interface, the integrator would have discretion to store the ECC codes directly and calculate integrator ECC codes for the data alone.

Figure: Example machine check reliability implementation

Error detection and logging

- Caliptra Subsystem IP shall interface to ECC protected memories.

- Caliptra Subsystem IP calculates and applies its own ECC code, which produces a total of 39-bit data written to external or INTEGRATOR instantiated SRAMs.

- Each 39-bit bank memory internally calculates 8-bit ECC on a write and stores 47 bits of data with ECC into SRAM.

- On read access syndrome is calculated based on 39-bit data.

- If parity error is detected and syndrome is valid, then the error is deemed single-bit and correctable.

- If no parity error is detected but syndrome == 0 or the syndrome is invalid, the error is deemed uncorrectable.

- On both single and double errors, the read data is modified before being returned to Caliptra Subsystem.

- Since single-bit errors shall be corrected through INTEGRATOR instantiated logic, Caliptra Subsystem never sees single-bit errors from SRAM.

- Double-bit or uncorrectable errors would cause unpredictable data to be returned to Caliptra Subsystem. Since this condition shall be detected and reported to MCRIP, there is no concern or expectation that Caliptra Subsystem will operate correctly after a double error.

- On detection, single errors are reported as transparent to MCRIP, double errors are reported as fatal.

- Along with error severity, MCRIP logs physical location of the error.

- After MCRIP logs an error, it has a choice to send out in-band notification to an external agent.

- MCRIP logs can be queried by SoC software.

Error injection

- MCRIP supports two error injection modes: intrusive and non-intrusive.

- Intrusive error injection:

- Can force a single or double error to be injected, which would result in incorrect data to be returned on read access.

- The intrusive error injection mode is disabled in Production fused parts via Security State signal.

- Non-intrusive error injection:

- Allows external software to write into MCRIP error log registers.

- The non-intrusive error injection does not interfere with the operation of memories.

- The non-intrusive error injection is functional in Production fused parts.

Caliptra Subsystem error handling flow

- Any implementation of error and recovery flows must adhere to the error handling requirements specified in Caliptra.md

- See MCI error handling for more details on MCI error infrastructure and error handling in Caliptra Subsystem.

- SoC level reporting and handling of fatal & non-fatal errors is product-specific architecture, outside the scope of Caliptra Subsystem definition. For example, a CPU and a PCIe device may handle fatal and non-fatal errors differently.

Programming interface

There are two primary programming avenues to interface with the Caliptra Subsystem:

-

MCU Firmware

- Description: This method involves programming the Microcontroller Unit (MCU) to execute firmware.

- Details: For more information on how to program the MCU and execute firmware via the MCU, please refer to the MCU Programming Interface documentation.

-

Caliptra Firmware

- Description: This method involves programming the Caliptra Core to execute firmware.

- Details: For more information on how to program and execute Caliptra Core firmware, please refer to the Caliptra Core References and Related Specifications.

Sequences

Reset Sequence:

- De-assert

cptra_ss_rst_b_iafter the primary clock (clk_i) stabilizes.

How to test

Reference tests are available at caliptra-ss\src\integration\test_suites

| Test Suite Name | Description |

|---|---|

MCU_HELLO_WORLD | Runs a basic "Hello World" program on the MCU to verify basic operation. |

MCU_CPTRA_BRINGUP | Tests the bring-up sequence of the MCU in the Caliptra Subsystem. |

MCU_DCCM_ACCESS | Validates access to the Data Closely Coupled Memory (DCCM) by the MCU. |

MCU_FUSE_CTRL_BRINGUP | Tests the bring-up sequence of the Fuse Controller by the MCU. |

MCU_LMEM_EXE | Tests execution by MCU from the MCU SRAM, contained inside the MCI component. LMEM refers to Local Memory, a generic alias for MCU SRAM. |

MCU_MCTP_SMOKE_TEST | Test verifies the I3C main target operation |

MCU_TEST_ROM_I3C_STREAMING_BOOT | Test verifies the I3C recovery target operation by using caliptra test ROM |

FUSE_PROV_WITH_LC_CTRL | Tests fuse provisioning in conjunction with the Lifecycle Controller. |

CALIPTRA_SS_LC_CTRL_BRINGUP | Tests the bring-up sequence of the Lifecycle Controller. |

CALIPTRA_SS_LC_CTRL_ST_TRANS | Validates state transitions of the Lifecycle Controller. |

Caliptra Core

Follow the link for Caliptra Core Integration Specification

MCU (Manufacturer Control Unit)

Overview

MCU is encapsulates VeeR EL2 core that includes an iCache, a dedicated DCCM, and AXI interfaces with separate AXI USER IDs to ROM and MCI. For more details refer to RISCV VeeR-EL2 Overview

Parameters & Defines

The VeeR EL2 core instance used for MCU has been configured with these options:

- DCCM size: 16KiB (see MCU DCCM SRAM Sizing)

- I-Cache depth: 16KiB

- ICCM: Disabled

- External Interrupt Vectors: 255

The following files from the Caliptra Subsystem repository contain the MCU configuration. Review these files for comprehensive list of MCU capabilities.

src/riscv_core/veer_el2/rtl/defines/css_mcu0_common_defines.vh

src/riscv_core/veer_el2/rtl/defines/css_mcu0_el2_param.vh

src/riscv_core/veer_el2/rtl/defines/css_mcu0_el2_pdef.vh

src/riscv_core/veer_el2/rtl/defines/defines.h

MCU Integration Requirements

-

Ensure Proper Memory Mapping

- The memory layout must match the physical memory configuration of the SoC.

- If modifications are required, update the base addresses and section placements accordingly.

- The address regions assigned to PIC and DCCM must not include any other AXI subordinates on the interconnect.

-

Enabling Programming interface.

- Please refer to section MCU Programming Interface for details on reference linker file for the MCU bringup.

MCU Core Configuration Customization

The MCU VeeR-EL2 core can be customized by integrators to optimize for specific SoC requirements.

Common Use Cases:

- Memory Architecture: Modify ICCM/DCCM addresses and sizes for SoC memory integration

- Power/Area Optimization: Remove or modify features (caching, number of interrupts)

- Performance Tuning: Adjust cache sizes and pipeline configurations for application workloads

Configuration Instructions:

Refer to the MCU Veer-EL2 Core Configuration section in the project README for complete step-by-step procedures.

Validation:

Execute the full regression test suite documented in How to test after any configuration changes to ensure system compatibility.

MCU DCCM SRAM Sizing

MCU's DCCM SRAM should be sized large enough to accommodate FW's stack and heap. If it is undersized, the MCU would have to rely on the MCU SRAM (accessed via AXI) for the stack/heap which has much lower performance.

MCU SRAM MRAC Considerations

The MCU's Memory Region Access Control (MRAC) regions are hard coded to 256MB boundaries. Each 256MB region is configured with uniform attributes - everything within a region is labeled as either "side effect" or "cacheable". This affects how MCU SRAM and MCU MBOX SRAM (both located within MCI) should be integrated into the SoC memory map, as different components within MCI may require different access attributes.

Split Memory Mapping

Integrators have two main approaches for handling MCI memory mapping:

Option 1: Contiguous MCI Address Region - If integrators don't care about the MRAC limitations described in the following sections, they can use a standard contiguous MCI address map where all MCI components (including MCU SRAM and MCU MBOX SRAM) reside within a single 256MB region.

Option 2: Split Memory Mapping - Integrators can optionally split MCU SRAM and MCU MBOX SRAMs into their own dedicated 256MB regions, separate from other MCI components. This allows firmware to enable caching or disable side effects for these specific SRAMs.

Side Effect Considerations

When MCU SRAM and MCU MBOX SRAM remain within the main MCI address space (not split off), integrators should consider the following access limitations:

DWORD Access Requirement: MCI peripherals (MCI CSRs, MCU trace buffer CSRs, etc) require "side effect" attribute enabled. When "side effect" is enabled dword-aligned accesses are required. Unaligned accesses, like accessing a uint8_t, are not permitted and will result in a read fault error in the MCU.

If you want to avoid these DWORD alignment limitations and allow more flexible access patterns, you can choose to implement the Split Memory Mapping (Option 2) in your AXI interconnect for MCU SRAM and/or MCU MBOX SRAM. This allows the SRAMs to be placed in regions without the side effect attribute.

iCache Considerations

When MCU SRAM remains within the main MCI address space (not split off), integrators should consider the following caching limitations:

iCache Enablement Requirement: To enable MCU iCache, everything within the 256MB boundary containing MCU SRAM must be cacheable. Since not all regions of MCI are cacheable, MCU iCache cannot be enabled when using a contiguous MCI address map.

If you want to enable MCU iCache functionality, you must implement the Split Memory Mapping (Option 2) in your AXI interconnect. This allows MCU SRAM to be placed in a dedicated cacheable region separate from other MCI components.

MCU Programming interface

MCU Linker Script Integration

This linker script defines the memory layout for the MCU firmware. It specifies the placement of various sections, ensuring proper memory mapping and execution flow.

Example Linker File can be found at : integration/test_suite/libs/riscv_hw_if/link.ld

By following this linker script configuration, the validation firmware can be correctly mapped and executed within the Caliptra Subsystem. Memory mapping for the validation firmware follows these principles:

- Instructions are stored in ROM for initial boot (.text)

- Read-only data is stored in ROM

- Stack and data sections are allocated to DCCM

- MCU SRAM is used for any combination of instructions and data to demonstrate program execution, data storage and persistence, streaming boot operations, and region protections that are enforced by MCI. Test firmware and corresponding linker scripts may be found in the repository test suites directory.

MCU External Interrupt Connections

| External interrupt vector | Description |

|---|---|

| 1 | MCI interrupts see MCI interrupt spec and MCI interrupt registers |

| 2 | I3C Interrupts |

| 255:3 | Exposed to SOC via cptra_ss_mcu_ext_int |

Fuse Controller

Overview

The Fuse Controller is a core component in the secure infrastructure of the system, responsible for managing the fuses and ensuring the integrity, consistency, and secure storage of sensitive data. It provides essential interfaces for direct fuse programming. The Fuse Controller interacts closely with the Lifecycle Controller (LC), FUSE macros, MCI, and Caliptra Core.

For an in-depth understanding of the Fuse Controller's functionality, including its programming flow, refer to Caliptra Subsystem Hardware Specification Document.

Parameters & Defines

| Parameter | Default | Description |

|---|---|---|

AlertAsyncOn | 5 | Enables asynchronous transitions on alerts. |

MemInitFile | "" | Hex file to initialize the OTP macro, including ECC. |

Interface

| Facing | Type | Width | Name | External Name in SoC Level | Description |

|---|---|---|---|---|---|

| External | Input | 1 | clk_i | cptra_ss_clk_i | Fuse Controller clock input. |

| External | Input | 1 | rst_ni | cptra_ss_rst_b_i | Reset signal input, active low. |

| Internal | Input | 1 | FIPS_ZEROIZATION_CMD_i | Fuse Zeroization signal controlled by MCI | |

| External | interface | 1 | core_axi_wr_req | cptra_ss_otp_core_axi_wr_req_i | AXI write request. |

| External | interface | 1 | core_axi_wr_rsp | cptra_ss_otp_core_axi_wr_rsp_o | AXI write response. |

| External | interface | 1 | core_axi_rd_req | cptra_ss_otp_core_axi_rd_req_i | AXI read request. |

| External | interface | 1 | core_axi_rd_rsp | cptra_ss_otp_core_axi_rd_rsp_o | AXI read response. |

| Internal | Output | 1 | intr_otp_operation_done_o | Indicates that the OTP operation has completed. | |

| Internal | Output | 1 | intr_otp_error_o | OTP error interrupt output (to be connected to MCI). | |

| Internal | Output | 5 | alerts | Alert signals for critical errors. | |

| Internal | Input | 1 | pwr_otp_i | OTP initialization request from the power manager. | |

| Internal | Output | Struct | pwr_otp_o | OTP response to the power manager. | |

| Internal | Input | Struct | lc_otp_vendor_test_i | Vendor test request input from LC Controller. | |

| Internal | Output | Struct | lc_otp_vendor_test_o | Vendor test response to LC Controller. | |

| Internal | Input | Struct | lc_otp_program_i | Lifecycle OTP programming request from LC Controller. | |

| Internal | Output | Struct | lc_otp_program_o | Lifecycle OTP programming response to LC Controller. | |

| Internal | Input | 1 | lc_dft_en_i | DFT enable input from LC Controller. | |

| Internal | Input | 1 | lc_escalate_en_i | Escalation enable input from LC Controller. | |

| Internal | Input | 1 | lc_check_byp_en_i | Clock bypass check enable input from LC Controller. | |

| Internal | Output | Struct | otp_lc_data_o | Lifecycle broadcasted data output to LC Controller. | |

| Internal | Output | Struct | otp_broadcast_o | FUSE broadcast output to Caliptra Core. This port broadcasts UDS-seed and Field-entropy-seed. |

Fuse Macro Memory Map and Fuse Controller CSR Address Map

The Caliptra Subsystem fuse controller supports a flexible and extensible memory map for storing one-time programmable (OTP) data. This structure is documented in the following files: See Fuse Controller Register Map for registers. See Fuse Macor Memory Map for fuse partition map.

The current fuse memory map consists of three main architectural segments: Caliptra-Core (prefix: CALIPTRA_CORE), Caliptra-Subsystem (prefix: CALIPTRA_SS), SoC/Vendor-Specific.

This structure enables separation of responsibilities and flexibility in SoC integration. While the Caliptra-Core fuse items are mandatory and must adhere to the Caliptra Fuse Map Specification, Caliptra-Subsystem fuses are required only when the subsystem is instantiated with Caliptra Subsystem. These Caliptra Subsystem fuses can also be configured based on SoC requirements. The SoC/Vendor-specific items can be customized based on integrator needs and product requirements. Therefore, the fields under SoC-specific categories can be resized or eliminated if unused.

SOC_SPECIFIC_IDEVID_CERTIFICATE Usage

This field defaults to 4 bytes but can be extended to accommodate storage of a full IDevID hybrid certificate (e.g., ML-DSA + ECC) if desired. Integrators must adjust its size in the YAML config used by the generation script.

FC Integration Requirements

Connectivity, Clock & Reset, Constraints & Violations

-

Connectivity:

- The Fuse Controller must interface seamlessly with the Fuse Macros, ensuring proper ECC support during programming and read operations.

- All AXI interfaces (

core_axi_wr_req,core_axi_rd_req) must follow the protocol specifications. - Inputs like

lc_otp_program_iandpwr_otp_ishould connect properly to the Lifecycle Controller (LC) and MCI respectively. - Alerts must propagate correctly to the system's alert manager for error handling.

-

Constraints & Violations:

- Any access to fuses must be gated by the

FUSE_CTRL_DIRECT_ACCESS_REGWENbit to prevent unauthorized writes. - There are some fuses that can be programmed only by Caliptra Core. Therefore, each AXI write should follow the access permission rule defined by

access_control_tableinsrc/fuse_ctrl/rtl/otp_ctrl_pkg.sv. - Timeout conditions during consistency checks (

FUSE_CTRL_CHECK_TIMEOUT) should trigger appropriate alerts. - Errors like invalid data, ECC failures, or access violations should raise alerts via the

alertssignal.

- Any access to fuses must be gated by the

-

Scan Path Exclusions:

- Ensure that secret fuse fields (UDS and Field-Entropy) and their corresponding flip-flops are not a parth of the scan path. Specifically, in this version, there are five OTP partitions that contain secrets that must not be leaked:

SECRET_MANUF_PARTITION: that contains the UDS seed, andSECRET_PROD_PARTITION_{0,1,2,3}: that each contain field entropy. These fuse partitions are "Buffered" partitions, meaning they are sensed at power-on and buffered in flip-flops until the next reset. During SoC integration it is vital to exclude the buffering flops that hold sensitive secret data from the scan chain to avoid leaks. These buffering flops may be excluded from the scan chain by excluding the following hierarchies:**::u_otp_ctrl::u_part_buf::u_otp_ctrl_ecc_reg::gen_partitions[X]::gen_buffered::u_part_buf::u_otp_ctrl_ecc_reg::**, for all values ofXin 1–5, since indices 1–5 map to the sensitive partitions mentioned above (defined in thePartInfolocalparam inotp_ctrl_part_pkg.sv, autogenerated from the OTP memory map HJSON). Additionally, these secrets are broadcasted with this input port:otp_broadcast_o. Therefore, this port, its propagated signals, and its driver signals must also not be scannable.

- Ensure that secret fuse fields (UDS and Field-Entropy) and their corresponding flip-flops are not a parth of the scan path. Specifically, in this version, there are five OTP partitions that contain secrets that must not be leaked:

- Since Fuse Controller scrambles secret partition with PRESENT chipher, this chiper keys, autogenerated from the OTP memory map HJSON, must be excluded from the scan path. Although these values are parameters defined in

otp_ctrl_part_pkg.sv, the registers driven by these parameters must be excluded from the scan path. - Note, the LC token partitions are not considered secret as only the cSHAKE128 hashes of each token are stored, not the raw tokens themselves.

Direct Access Interface

Fuse macros has to be programmed via the Direct Access Interface, which is comprised of the following CSRs:

| CSR Name | Description |

|---|---|

DIRECT_ACCESS_WDATA_0 | Low 32bit word to be written. |

DIRECT_ACCESS_WDATA_1 | High 32bit word to be written. |

DIRECT_ACCESS_RDATA_0 | Low 32bit word that has been read. |

DIRECT_ACCESS_RDATA_1 | High 32bit word that has been read. |

DIRECT_ACCESS_ADDRESS | byte address for the access. |

DIRECT_ACCESS_CMD | Command register to trigger a read or a write access. |

DIRECT_ACCESS_REGWEN | Write protection register for DAI. |

Initialization

The OTP controller initializes automatically upon power-up and is fully operational by the time the processor boots. The only initialization steps that SW should perform are:

- Check that the OTP controller has successfully initialized by reading

STATUS. I.e., make sure that none of the ERROR bits are set, and that the DAI is idle (STATUS.DAI_IDLE).- Choose whether the periodic background checks shall be subject to a timeout by programming a nonzero timeout cycle count to

CHECK_TIMEOUT. In this case, theCHECK_TIMEOUTregister must be set before theINTEGRITY_CHECK_PERIODandCONSISTENCY_CHECK_PERIODregisters (see next point). - Enable periodic background checks by programming nonzero mask values to

INTEGRITY_CHECK_PERIODandCONSISTENCY_CHECK_PERIOD. - It is recommended to lock down the background check registers via

CHECK_REGWEN, once the background checks have been set up

- Choose whether the periodic background checks shall be subject to a timeout by programming a nonzero timeout cycle count to

If needed, one-off integrity and consistency checks can be triggered via CHECK_TRIGGER.

If this functionality is not needed, it is recommended to lock down the trigger register via CHECK_TRIGGER_REGWEN.

Programming interface

The Fuse Controller (FC) programming interface is designed to manage lifecycle states, handle fuses with ECC support, and ensure secure interactions with the fuse macros. A key component in this architecture is the Fuse Controller Filter RTL. This module intercepts and verifies the fuse programming sequence by checking that all parts of the transaction originate from the same authorized source. In doing so, the filter guarantees that fuse provisioning is performed in an atomic manner.

Atomic fuse provisioning means that only one entity can initiate the programming sequence at a time. The entire sequence—data write, address write, and command write—must complete successfully. If any phase fails or if an inconsistency is detected (for example, if the AXI user ID changes between phases), the operation is aborted, and a cold reset is required before any new programming attempt can be made.

The access control table, which defines allowed fuse address ranges along with the corresponding authorized AXI user IDs. See access_control_table in src/fuse_ctrl/rtl/otp_ctrl_pkg.sv.

Below are the key operations supported by the programming interface:

-

Direct Access Interface (DAI):

- Registers:

FUSE_CTRL_DIRECT_ACCESS_CMD: Specifies the operation (FUSE_CTRL_CMD_DAI_WRITEfor write,FUSE_CTRL_CMD_DAI_READfor read).FUSE_CTRL_DIRECT_ACCESS_ADDRESS: Specifies the fuse memory address to access.FUSE_CTRL_DIRECT_ACCESS_WDATA_0: Write data (32-bit granularity).FUSE_CTRL_DIRECT_ACCESS_WDATA_1: Write data for 64-bit operations.FUSE_CTRL_DIRECT_ACCESS_RDATA_0: Read data (32-bit granularity).FUSE_CTRL_DIRECT_ACCESS_RDATA_1: Read data for 64-bit operations.

- Procedure:

- Write the address to

FUSE_CTRL_DIRECT_ACCESS_ADDRESS. - For write operations:

- Populate

FUSE_CTRL_DIRECT_ACCESS_WDATA_0(andFUSE_CTRL_DIRECT_ACCESS_WDATA_1for 64-bit operations).

- Populate

- Set the command in

FUSE_CTRL_DIRECT_ACCESS_CMD. - Wait for the operation to complete by polling the

DAI_IDLEbit inFUSE_CTRL_STATUS.

- Write the address to

- ECC Support:

- ECC is automatically applied during programming to ensure data integrity.

- Registers:

-

Digest Calculation:

- Used to lock a partition after programming is complete.

- Registers:

FUSE_CTRL_DIRECT_ACCESS_CMD: Use command0x4for digest calculation.FUSE_CTRL_DIRECT_ACCESS_ADDRESS: Partition base address.

- Procedure:

- Write the partition base address to

FUSE_CTRL_DIRECT_ACCESS_ADDRESS. - Trigger the digest calculation command (

0x4) inFUSE_CTRL_DIRECT_ACCESS_CMD. - Poll the

DAI_IDLEbit inFUSE_CTRL_STATUSto confirm the operation is complete.

- Write the partition base address to

Readout Sequence

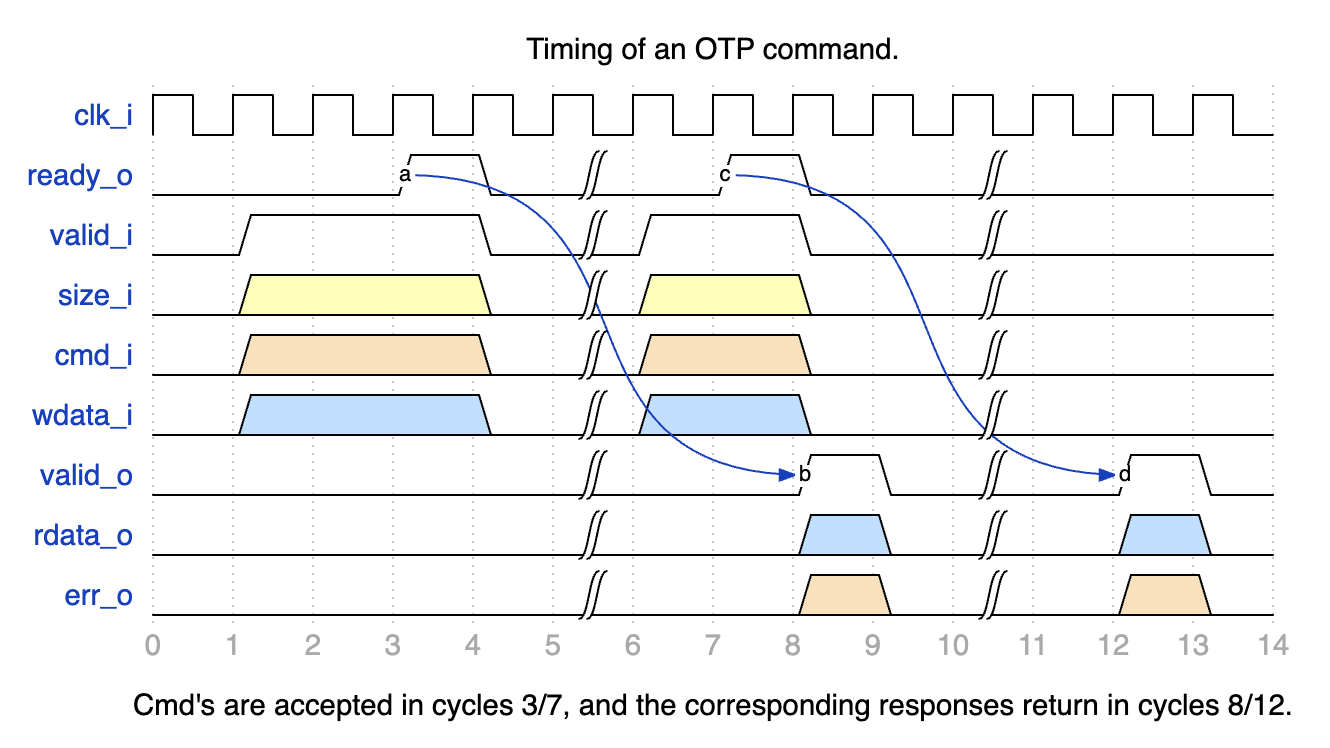

A typical readout sequence looks as follows:

- Check whether the DAI is idle by reading the

STATUSregister. - Write the byte address for the access to

DIRECT_ACCESS_ADDRESS. Note that the address is aligned with the granule, meaning that either 2 or 3 LSBs of the address are ignored, depending on whether the access granule is 32 or 64bit. - Trigger a read command by writing 0x1 to

DIRECT_ACCESS_CMD. - Poll the

STATUSuntil the DAI state goes back to idle. Alternatively, theotp_operation_doneinterrupt can be enabled up to notify the processor once an access has completed. - If the status register flags a DAI error, additional handling is required.

- If the region accessed has a 32bit access granule, the 32bit chunk of read data can be read from

DIRECT_ACCESS_RDATA_0. If the region accessed has a 64bit access granule, the 64bit chunk of read data can be read from theDIRECT_ACCESS_RDATA_0andDIRECT_ACCESS_RDATA_1registers. - Go back to the first step and repeat until all data has been read.

The hardware will set DIRECT_ACCESS_REGWEN to 0x0 while an operation is pending in order to temporarily lock write access to the CSRs registers.

Sequences: Reset, Boot

-

Reset Sequence:

- De-assert

rst_niafter the primary clock (clk_i) stabilizes. - Verify reset state by reading

FUSE_CTRL_STATUS. All errors in the status register should be 0. - Ensure Fuse Macros are in their default state after reset.

- De-assert

-

Boot Sequence:

- Initialize Fuse Macros by programming essential fuses using the programming interface.

- Perform a full integrity check by triggering

FUSE_CTRL_CHECK_TRIGGERand ensure the system is error-free before proceeding. - Validate readiness by checking the

FUSE_CTRL_STATUSregister.

How to test : Smoke & more

The smoke test focuses on ensuring basic functionality and connectivity of the FC & LCC. TODO More details will be provided once FC is ready to test.

Generating the Fuse Partitions

The configurable parts of the fuse_ctrl, specifically the fuse map and register interface,

are bootstrapped through a separate script ./tools/scripts/fuse_ctrl_script/gen_fuse_ctrl_partitions.py.

For a detailed breakdown of the design rationale behind the script as well as execution instructions,

refer to Fuse Map Generation Script.

Fuse Controller Macro

The following integration section is based on the Generalized Open-source Interface with modifications to match the Caliptra implementation.

Overview

The Fuse Controller Macro implements a generalized open-source interface for functional operation (described below). Any OTP redundancy mechanism like per-word ECC is assumed to be handled inside the wrapper, which means that the word width exposed as part of the generalized interface is the effective word width.

Paramteres & Defines

| Parameter | Default | Description |

|---|---|---|

Width | 16 | Width of native OTP words. |

AddrWidth | Derived | Width of the address signal, derived from Depth. |

Depth | `2**OtpAddrWidth | Depth of OTP macro. |

CmdWidth | 7 | Width of the OTP command. Sparsely encoded. |

ErrWidth | 3 | Width of error code output signal. |

SizeWidth | 2 | Width of the size input field. Allows to transfer up to 4 native OTP words at once. |