v2.0: image10.png

v2.1: image10.png

Image not present in this version

| @@ -1,3354 +1,90 @@ | |||

| 1 | 1 | <div style="font-size: 0.85em; color: #656d76; margin-bottom: 1em; padding: 0.5em; background: #f6f8fa; border-radius: 4px;"> | |

| 2 | -📄 Source: <a href="https://github.com/chipsalliance/adams-bridge/blob/c6eacc84c4466348950d7a6a449efb913596795c/docs/AdamsBridgeHardwareSpecification.md" target="_blank">chipsalliance/adams-bridge/docs/AdamsBridgeHardwareSpecification.md</a> @ <code>c6eacc8</code> | ||

| 2 | +📄 Source: <a href="https://github.com/chipsalliance/adams-bridge/blob/85aef2e247eb7c08ce4d41cf41709eedb3e6b1ee/docs/AdamsBridgeHardwareSpecification.md" target="_blank">chipsalliance/adams-bridge/docs/AdamsBridgeHardwareSpecification.md</a> @ <code>85aef2e</code> | ||

| 3 | 3 | </div> | |

| 4 | 4 | ||

| 5 | 5 |  | |

| 6 | 6 | ||

| 7 | 7 | <p style="text-align: center;">Adam's Bridge Hardware Specification</p> | |

| 8 | 8 | ||

| 9 | -<p style="text-align: center;">Version 1.0.2</p> | ||

| 9 | +<p style="text-align: center;">Version 1.0</p> | ||

| 10 | 10 | ||

| 11 | 11 | <div style="page-break-after: always"></div> | |

| 12 | 12 | ||

| 13 | 13 | # Scope | |

| 14 | 14 | ||

| 15 | -This document defines technical specifications for a Adam's Bridge Post-Quantum Cryptography (PQC ML-DSA) subsystem used in the Open Compute Project (OCP). This document shall comprise the Adam's Bridge technical specification. | ||

| 15 | +This document defines technical specifications for a Adam's Bridge Post-Quantum Cryptography (PQC ML-DSA and ML-KEM) subsystem used in the Open Compute Project (OCP). This document shall comprise the Adam's Bridge technical specification. | ||

| 16 | 16 | ||

| 17 | 17 | # Overview | |

| 18 | 18 | ||

| 19 | -This document provides definitions and requirements for a Adam's Bridge Post-Quantum Cryptography (PQC ML-DSA) subsystem. The document then relates these definitions to existing technologies, enabling device and platform vendors to better understand those technologies in trusted computing terms. | ||

| 19 | +This document provides definitions and requirements for a Adam's Bridge Post-Quantum Cryptography (PQC ML-DSA and ML-KEM) subsystem. The document then relates these definitions to existing technologies, enabling device and platform vendors to better understand those technologies in trusted computing terms. | ||

| 20 | 20 | ||

| 21 | 21 | # Introduction | |

| 22 | 22 | ||

| 23 | 23 | The advent of quantum computers poses a serious challenge to the security of cloud infrastructures and services, as they can potentially break the existing public-key cryptosystems, such as RSA and elliptic curve cryptography (ECC). Even though the gap between today’s quantum computers and the threats they pose to current public-key cryptography is large, the cloud landscape should act proactively and initiate the transition to the post-quantum era as early as possible. To comply with that, the U.S. government issued a National Security Memorandum in May 2022 that mandated federal agencies to migrate to PQC by 2035 \[1\]. | |

| 24 | 24 | ||

| 25 | -The long-term security of cloud computing against quantum attacks depends on developing lattice-based cryptosystems, which are among the most promising PQC algorithms that are believed to be hard for both classical and quantum computers. The American National Institute of Standards and Technology (NIST) recognized this and selected CRYSTALS-KYBER (ML-KEM) and CRYSTALS-Dilithium (ML-DSA) \[2\], two lattice-based algorithms, as standards for post-quantum key-establishment and digital signatures, respectively, in July 2022\. These cryptosystems are constructed on the hardness of the module learning-with-errors problem (M-LWE) in module lattices. | ||

| 25 | +The long-term security of cloud computing against quantum attacks depends on developing lattice-based cryptosystems, which are among the most promising PQC algorithms that are believed to be hard for both classical and quantum computers. The American National Institute of Standards and Technology (NIST) recognized this and selected CRYSTALS-KYBER (ML-KEM) \[2\] and CRYSTALS-Dilithium (ML-DSA) \[3\], two lattice-based algorithms, as standards for post-quantum key-establishment and digital signatures, respectively, in July 2022\. These cryptosystems are constructed on the hardness of the module learning-with-errors problem (M-LWE) in module lattices. | ||

| 26 | 26 | ||

| 27 | 27 | To transition to PQC, we must develop hybrid cryptosystems to maintain industry or government regulations, while PQC updates will be applied thoroughly. Therefore, classical cryptosystems, e.g. ECC, cannot be eliminated even if PQC will significantly be developed. | |

| 28 | 28 | ||

| 29 | 29 | Adam’s bridge was a mythological structure that existed to cross the formidable gulf that existed between two land masses. Asymmetric cryptography to post quantum is a similar formidable gap that exists in the world of cryptography and Adam’s bridge is the work undertaken to bridge the gap by building post quantum cryptographic accelerators. | |

| 30 | 30 | ||

| 31 | -In this presentation, we share the architectural characteristics of our post-quantum Adams Bridge implementation. Our proposed work divides the operations in the algorithms into multiple stages and executes them using pipelined processing architecture. We use an optimized cascading method within each stage and fine-tune each module individually to exploit multi-levels of parallelism to accelerate post-quantum Dilithium computation on hardware platforms to address performance and complexity challenges of PQC implementation. Our proposed architecture uses various optimization techniques, including multi-levels of parallelism, designing reconfigurable cores, and implementing interleaved and pipelined architecture achieving significant speedup while maintaining high security and scalability. Our work can facilitate the adoption and deployment of PQC in cloud computing and enhance the security and efficiency of cloud services and applications in the post-quantum era. | ||

| 31 | +This document shares the architectural characteristics of the proposed post-quantum Adams Bridge implementation. The proposed work divides the operations in the algorithms into multiple stages and executes them using pipelined processing architecture. An optimized cascading method is used within each stage and fine-tune each module individually to exploit multi-levels of parallelism to accelerate post-quantum Dilithium computation on hardware platforms to address performance and complexity challenges of PQC implementation. The proposed architecture uses various optimization techniques, including multi-levels of parallelism, designing reconfigurable cores, and implementing interleaved and pipelined architecture achieving significant speedup while maintaining high security and scalability. This work can facilitate the adoption and deployment of PQC in cloud computing and enhance the security and efficiency of cloud services and applications in the post-quantum era. | ||

| 32 | 32 | ||

| 33 | -# High-Level Overview | ||

| 33 | +# Documentation | ||

| 34 | 34 | ||

| 35 | -Adam’s Bridge accelerator has all the necessary components to execute a pure hardware PQC operation. The main operations that involve more computational complexity, such as NTT, hashing, and sampling units, are explained as follows. | ||

| 35 | +The project contains comprehensive documentation of all submodules for ML-DSA and ML-KEM: | ||

| 36 | 36 | ||

| 37 | -  | ||

| 37 | +- [ML-DSA Documentation](./AdamsBridge_MLDSA.md) | ||

| 38 | +- [ML-KEM Documentation](./AdamsBridge_MLKEM.md) | ||

| 38 | 39 | ||

| 39 | -The security level of ML-DSA defined by NIST are as follows: | ||

| 40 | +# Memory requirement | ||

| 40 | 41 | ||

| 41 | -| Algorithm Name | Security Level | | ||

| 42 | -| :------------- | :------------- | | ||

| 43 | -| ML-DSA-44 | Level-2 | | ||

| 44 | -| ML-DSA-65 | Level-3 | | ||

| 45 | -| **ML-DSA-87** | **Level-5** | | ||

| 46 | - | ||

| 47 | - | ||

| 48 | -CNSA 2.0 only allows the highest security level (Level-5) for PQC which is ML-DSA-87, and **Adams Bridge only supports ML-DSA-87 parameter set.** | ||

| 49 | - | ||

| 50 | -# API | ||

| 51 | - | ||

| 52 | -The ML-DSA-87 architecture inputs and outputs are described in the following table. | ||

| 53 | - | ||

| 54 | - | ||

| 55 | -| Name | Input/Output | Operation | Size (Byte) | | ||

| 56 | -| --------------------------- | --------------- | --------------- | ------------- | | ||

| 57 | -| name | Output | All | 8 | | ||

| 58 | -| version | Output | All | 8 | | ||

| 59 | -| ctrl | Input | All | 4 | | ||

| 60 | -| status | Output | All | 4 | | ||

| 61 | -| entropy (SCA) | Input | All | 64 | | ||

| 62 | -| seed | Input | Keygen | 32 | | ||

| 63 | -| sign\_rnd | Input | Sign | 32 | | ||

| 64 | -| message | Input | Sign/Verify | 64 | | ||

| 65 | -| verification result | Output | Verify | 64 | | ||

| 66 | -| External_Mu | Input | Sign/Verify | 64 | | ||

| 67 | -| message strobe | Input | Sign/Verify | 1 | | ||

| 68 | -| ctx size | Input | Sign/Verify | 1 | | ||

| 69 | -| ctx | Input | Sign/Verify | 255 (+1) | | ||

| 70 | -| pk | Input/Output | Keygen/Verify | 2592 | | ||

| 71 | -| signature | Input/Output | Sign/Verify | 4627 (+1) | | ||

| 72 | -| sk\_out (software only) | Output | Keygen | 4896 | | ||

| 73 | -| sk\_in | Input | Signing | 4896 | | ||

| 74 | -| Interrupt | Output | All | 520 | | ||

| 75 | -| --------------------------- | --------------- | --------------- | ------------- | | ||

| 76 | -| Total ||| 18440 | | ||

| 77 | - | ||

| 78 | - | ||

| 79 | -## name | ||

| 80 | - | ||

| 81 | -Read-only register consists of the name of component. | ||

| 82 | - | ||

| 83 | -## version | ||

| 84 | - | ||

| 85 | -Read-only register consists of the version of component. | ||

| 86 | - | ||

| 87 | -## CTRL | ||

| 88 | - | ||

| 89 | -The control register consists of the following flags: | ||

| 90 | - | ||

| 91 | -| Bits | Identifier | Access | Reset | Decoded | Name | | ||

| 92 | -| :------- | :---------- | :----- | :---- | :------ | :--- | | ||

| 93 | -| \[31:7\] | \- | \- | \- || \- | | ||

| 94 | -| \[6\] | STREAM_MSG | w | 0x0 || \- | | ||

| 95 | -| \[5\] | EXTERNAL_MU | w | 0x0 || \- | | ||

| 96 | -| \[4\] | PCR_SIGN | w | 0x0 || \- | | ||

| 97 | -| \[3\] | ZEROIZE | w | 0x0 || \- | | ||

| 98 | -| \[2:0\] | CTRL | w | 0x0 || \- | | ||

| 99 | - | ||

| 100 | - | ||

| 101 | -### CTRL | ||

| 102 | - | ||

| 103 | -CTRL command field contains two bits indicating: | ||

| 104 | - | ||

| 105 | -* Ctrl \= 0b000 | ||

| 106 | - | ||

| 107 | -No Operation. | ||

| 108 | - | ||

| 109 | -* Ctrl \= 0b001 | ||

| 110 | - | ||

| 111 | -Trigs the core to start the initialization and perform keygen operation. | ||

| 112 | - | ||

| 113 | -* Ctrl \= 0b010 | ||

| 114 | - | ||

| 115 | -Trigs the core to start the signing operation for a message block. | ||

| 116 | - | ||

| 117 | -* Ctrl \= 0b011 | ||

| 118 | - | ||

| 119 | -Trigs the core to start verifying a signature for a message block. | ||

| 120 | - | ||

| 121 | -* Ctrl \= 0b100 | ||

| 122 | - | ||

| 123 | -Trigs the core to start the keygen+signing operation for a message block. This mode decreases storage costs for the secret key (SK) by recalling keygen and using an on-the-fly SK during the signing process. | ||

| 124 | - | ||

| 125 | -### ZEROIZE | ||

| 126 | - | ||

| 127 | -Zeroize all internal registers: Zeroize all internal registers after process to avoid SCA leakage. | ||

| 128 | -Firmware write generates only a single-cycle pulse on the hardware interface and then will be erased. | ||

| 129 | -Zeroization operation requires 1,408 clock cycles to clear the SRAMs. Firmware must query for the ready status bit to be asserted before issuing another command. | ||

| 130 | - | ||

| 131 | -### PCR_SIGN | ||

| 132 | - | ||

| 133 | -Run PCR Signing flow: Run MLDSA KeyGen+Signing flow to sign PCRs. | ||

| 134 | - | ||

| 135 | -### EXTERNAL_MU | ||

| 136 | - | ||

| 137 | -Enable External_Mu Mode. (this mode is hard turned off for now.) | ||

| 138 | -The External_mu variant of ML-DSA modifies the standard signing and verifying process by allowing the precomputed mu to be externally provided instead of being internally derived from the message and public key. In this variant, the signing procedure accepts mu as an explicit input, making it suitable for environments where mu is generated offline for efficiency. While the core signing and verifying algorithm remains unchanged, the message input register is ignored in this mode. | ||

| 139 | - | ||

| 140 | -### STREAM_MSG | ||

| 141 | - | ||

| 142 | -Enable streaming message mode. | ||

| 143 | - | ||

| 144 | -In this mode, the controller will wait until it requires the message data and will assert the MSG_STREAM_READY bit in the status register. Once MSG_STREAM_READY is observed, the user should first set MSG_STROBE to 0xF. | ||

| 145 | - | ||

| 146 | -The user can then write the message, one dword at a time, by writing to dword 0 of the message register. If the last dword is partial, the user must set the MSG_STROBE register to appropriately indicate the valid bytes. If the message is dword-aligned, a value of 0x0 must be written to the MSG_STROBE register to indicate the last dword, followed by a dummy write to the message register. | ||

| 147 | - | ||

| 148 | -The flow must be terminated by writing to the message register after setting the MSG_STROBE to a non 0xF value. | ||

| 149 | -No partial dwords are allowed before the last dword indication. | ||

| 150 | -MSG_STROBE only needs to be programmed before the stream of full dwords, and before the final dword. | ||

| 151 | -Valid values of MSG_STROBE include 4'b1111, 4'b0111, 4'b0011, 4'b0001, and 4'b0000. | ||

| 152 | - | ||

| 153 | -## status | ||

| 154 | - | ||

| 155 | -The read-only status register consists of the following flags: | ||

| 156 | - | ||

| 157 | -| Bits | Identifier | Access | Reset | Decoded | Name | | ||

| 158 | -| :------- | :--------- | :----- | :---- | :------ | :--- | | ||

| 159 | -| \[31:3\] | \- | \- | \- || \- | | ||

| 160 | -| \[2\] | MSG_STREAM_READY | r | 0x0 || \- | | ||

| 161 | -| \[1\] | VALID | r | 0x0 || \- | | ||

| 162 | -| \[0\] | READY | r | 0x0 || \- | | ||

| 163 | - | ||

| 164 | - | ||

| 165 | -### READY | ||

| 166 | - | ||

| 167 | -Indicates if the core is ready to process the inputs. | ||

| 168 | - | ||

| 169 | -### VALID | ||

| 170 | - | ||

| 171 | -Indicates if the process is computed and the output is valid. | ||

| 172 | - | ||

| 173 | -### MSG_STREAM_READY | ||

| 174 | - | ||

| 175 | -Indicates if the core is ready to process the message. | ||

| 176 | - | ||

| 177 | -## entropy | ||

| 178 | - | ||

| 179 | -Entropy is required for SCA countermeasures to randomize the inputs with no change in the outputs. The entropy can be any 512-bit value in \[0 : 2^512-1\]. | ||

| 180 | - | ||

| 181 | -The ML-DSA-87 countermeasure requires several random vectors to randomize the intermediate values. An internal mechanism is considered to take one random vector of 512-bit (i.e., entropy register) and generate the required random vectors for different countermeasures. | ||

| 182 | - | ||

| 183 | -## seed | ||

| 184 | - | ||

| 185 | -Adams Bridge component seed register type definition 8 32-bit registers storing the 256-bit seed for keygen. The seed can be any 256-bit value in \[0 : 2^256-1\]. | ||

| 186 | - | ||

| 187 | -## sign\_rnd | ||

| 188 | - | ||

| 189 | -This register is used to support both deterministic and hedge variants of ML-DSA. The content of this register is the only difference between the deterministic and hedged variant of ML-DSA. | ||

| 190 | - | ||

| 191 | -- In the “hedged” variant, sign\_rnd is the output of an RBG. | ||

| 192 | -- In the “deterministic” variant, sign\_rnd is a 256-bit string consisting entirely of zeroes. | ||

| 193 | - | ||

| 194 | -## message | ||

| 195 | - | ||

| 196 | -When not in streaming message mode, this architecture supports PureML-DSA defined by NIST with an empty ctx. | ||

| 197 | -When streaming message mode is enabled, this field is ignored except for dword 0 which is used to stream in the message. | ||

| 198 | - | ||

| 199 | -## verification result | ||

| 200 | - | ||

| 201 | -To mitigate a possible fault attack on Boolean flag verification result, a 64-byte register is considered. Firmware is responsible for comparing the computed result with a certain segment of signature (segment c\~), and if they are equal the signature is valid. | ||

| 202 | - | ||

| 203 | -## msg strobe | ||

| 204 | - | ||

| 205 | -A 4-bit indication of enabled bytes in the next dword of the streamed message. | ||

| 206 | -Users must first program this to 0xF after observing MSG_STREAM_READY, unless the message is less than 1 dword. | ||

| 207 | -If the final dword is partial, MSG_STROBE must be programmed appropriately before writing the final bytes. | ||

| 208 | -Dword aligned messages must program MSG_STROBE to 0x0 to indicate the message is done being streamed. | ||

| 209 | - | ||

| 210 | -## ctx size | ||

| 211 | - | ||

| 212 | -A 8-bit indication of the size in bytes of the ctx to be used. | ||

| 213 | - | ||

| 214 | -## ctx | ||

| 215 | - | ||

| 216 | -This register stores the ctx field. It is applied only during streaming message mode. | ||

| 217 | - | ||

| 218 | -## sk\_out | ||

| 219 | - | ||

| 220 | -This register stores the private key for keygen if seed is given by software. This register can be read by ML-DSA user, i.e., software, after keygen operation. | ||

| 221 | - | ||

| 222 | -If seed comes from the key vault, this register will not contain the private key to avoid exposing secret assets to software. | ||

| 223 | - | ||

| 224 | -## sk\_in | ||

| 225 | - | ||

| 226 | -This register stores the private key for signing. This register should be set before signing operation. | ||

| 227 | - | ||

| 228 | -## pk | ||

| 229 | - | ||

| 230 | -ML-DSA component public key register type definition storing the public key. This register can be read by Adams Bridge user after keygen operation, or be set before verifying operation. | ||

| 231 | - | ||

| 232 | -## signature | ||

| 233 | - | ||

| 234 | -ML-DSA component signature register type definition storing the signature of the message. This register is read by Adams Bridge user after signing operation, or be set before verifying operation. | ||

| 235 | - | ||

| 236 | -# Pseudocode | ||

| 237 | - | ||

| 238 | -## Keygen | ||

| 239 | - | ||

| 240 | -```cpp | ||

| 241 | -Input: | ||

| 242 | - seed | ||

| 243 | - entropy | ||

| 244 | - | ||

| 245 | -Output: | ||

| 246 | - sk_out | ||

| 247 | - pk | ||

| 248 | - | ||

| 249 | -// Wait for the core to be ready (STATUS flag should be 2'b01 or 2'b11) | ||

| 250 | -read_data = 0 | ||

| 251 | -while read_data == 0: | ||

| 252 | - read_data = read(ADDR_STATUS) | ||

| 253 | - | ||

| 254 | -// Feed the required inputs | ||

| 255 | -write(ADDR_SEED, seed) | ||

| 256 | -write(ADDR_ENTROPY, entropy) | ||

| 257 | - | ||

| 258 | -// Trigger the core for performing Keygen | ||

| 259 | -write(ADDR_CTRL, KEYGEN_CMD) // (STATUS flag will be changed to 2'b00) | ||

| 260 | - | ||

| 261 | -// Wait for the core to be ready and valid (STATUS flag should be 2'b11) | ||

| 262 | -read_data = 0 | ||

| 263 | -while read_data == 0: | ||

| 264 | - read_data = read(ADDR_STATUS) | ||

| 265 | - | ||

| 266 | -// Reading the outputs | ||

| 267 | -sk_out = read(ADDR_SK) | ||

| 268 | -pk = read(ADDR_PK) | ||

| 269 | - | ||

| 270 | -// Return the outputs | ||

| 271 | -return sk_out, pk | ||

| 272 | -``` | ||

| 273 | - | ||

| 274 | -## Signing | ||

| 275 | - | ||

| 276 | -```cpp | ||

| 277 | -Input: | ||

| 278 | - msg | ||

| 279 | - sk_in | ||

| 280 | - sign_rnd | ||

| 281 | - entropy | ||

| 282 | - | ||

| 283 | -Output: | ||

| 284 | - signature | ||

| 285 | - | ||

| 286 | -// Wait for the core to be ready (STATUS flag should be 2'b01 or 2'b11) | ||

| 287 | -read_data = 0; | ||

| 288 | -while (read_data == 0) { | ||

| 289 | - read_data = read(ADDR_STATUS); | ||

| 290 | -} | ||

| 291 | - | ||

| 292 | -// Feed the required inputs | ||

| 293 | -write(ADDR_MSG, msg); | ||

| 294 | -write(ADDR_SK_IN, sk_in); | ||

| 295 | -write(ADDR_SIGN_RND, sign_rnd); | ||

| 296 | -write(ADDR_ENTROPY, entropy); | ||

| 297 | - | ||

| 298 | -// Trigger the core for performing Signing | ||

| 299 | -write(ADDR_CTRL, SIGN_CMD); // (STATUS flag will be changed to 2'b00) | ||

| 300 | - | ||

| 301 | -// Wait for the core to be ready and valid (STATUS flag should be 2'b11) | ||

| 302 | -read_data = 0; | ||

| 303 | -while (read_data == 0) { | ||

| 304 | - read_data = read(ADDR_STATUS); | ||

| 305 | -} | ||

| 306 | - | ||

| 307 | -// Reading the outputs | ||

| 308 | -signature = read(ADDR_SIGNATURE); | ||

| 309 | - | ||

| 310 | -// Return the output (signature) | ||

| 311 | -return signature; | ||

| 312 | -``` | ||

| 313 | - | ||

| 314 | -## Verifying | ||

| 315 | - | ||

| 316 | -```cpp | ||

| 317 | -Input: | ||

| 318 | - msg | ||

| 319 | - pk | ||

| 320 | - signature | ||

| 321 | - | ||

| 322 | -Output: | ||

| 323 | - verification_result | ||

| 324 | - | ||

| 325 | -// Wait for the core to be ready (STATUS flag should be 2'b01 or 2'b11) | ||

| 326 | -read_data = 0; | ||

| 327 | -while (read_data == 0) { | ||

| 328 | - read_data = read(ADDR_STATUS); | ||

| 329 | -} | ||

| 330 | - | ||

| 331 | -// Feed the required inputs | ||

| 332 | -write(ADDR_MSG, msg); | ||

| 333 | -write(ADDR_PK, pk); | ||

| 334 | -write(ADDR_SIGNATURE, signature); | ||

| 335 | - | ||

| 336 | -// Trigger the core for performing Verifying | ||

| 337 | -write(ADDR_CTRL, VERIFY_CMD); // (STATUS flag will be changed to 2'b00) | ||

| 338 | - | ||

| 339 | -// Wait for the core to be ready and valid (STATUS flag should be 2'b11) | ||

| 340 | -read_data = 0; | ||

| 341 | -while (read_data == 0) { | ||

| 342 | - read_data = read(ADDR_STATUS); | ||

| 343 | -} | ||

| 344 | - | ||

| 345 | -// Reading the outputs | ||

| 346 | -verification_result = read(ADDR_VERIFICATION_RESULT); | ||

| 347 | - | ||

| 348 | -// Return the output (verification_result) | ||

| 349 | -return verification_result; | ||

| 350 | -``` | ||

| 351 | - | ||

| 352 | -## Keygen \+ Signing | ||

| 353 | - | ||

| 354 | -This mode decreases storage costs for the secret key (SK) by recalling keygen and using an on-the-fly SK during the signing process. | ||

| 355 | - | ||

| 356 | -```cpp | ||

| 357 | -Input: | ||

| 358 | - seed | ||

| 359 | - msg | ||

| 360 | - sign_rnd | ||

| 361 | - entropy | ||

| 362 | - | ||

| 363 | -Output: | ||

| 364 | - signature | ||

| 365 | - | ||

| 366 | -// Wait for the core to be ready (STATUS flag should be 2'b01 or 2'b11) | ||

| 367 | -read_data = 0; | ||

| 368 | -while (read_data == 0) { | ||

| 369 | - read_data = read(ADDR_STATUS); | ||

| 370 | -} | ||

| 371 | - | ||

| 372 | -// Feed the required inputs | ||

| 373 | -write(ADDR_SEED, seed); | ||

| 374 | -write(ADDR_MSG, msg); | ||

| 375 | -write(ADDR_SIGN_RND, sign_rnd); | ||

| 376 | -write(ADDR_ENTROPY, entropy); | ||

| 377 | - | ||

| 378 | -// Trigger the core for performing Keygen + Signing | ||

| 379 | -write(ADDR_CTRL, KEYGEN_SIGN_CMD); // (STATUS flag will be changed to 2'b00) | ||

| 380 | - | ||

| 381 | -// Wait for the core to be ready and valid (STATUS flag should be 2'b11) | ||

| 382 | -read_data = 0; | ||

| 383 | -while (read_data == 0) { | ||

| 384 | - read_data = read(ADDR_STATUS); | ||

| 385 | -} | ||

| 386 | - | ||

| 387 | -// Reading the outputs | ||

| 388 | -signature = read(ADDR_SIGNATURE); | ||

| 389 | - | ||

| 390 | -// Return the output (signature) | ||

| 391 | -return signature; | ||

| 392 | -``` | ||

| 393 | - | ||

| 394 | -# Performance and Area Results | ||

| 395 | - | ||

| 396 | -## ML-DSA-87 | ||

| 397 | - | ||

| 398 | -The performance results for two operational frequencies, 400 MHz and 600 MHz, are presented in terms of latency (clock cycles [CCs]), time [ms], and performance [IOPS] as follows: | ||

| 399 | - | ||

| 400 | -|| Freq [MHz] | 400 ||| 600 || | ||

| 401 | -| --------------------- | ---------------- | ------------: | ---------------------- | --- | ------------: | ---------------------- | | ||

| 402 | -| **"Unprotected"** | **Latency [CC]** | **Time [ms]** | **Performance [IOPS]** || **Time [ms]** | **Performance [IOPS]** | | ||

| 403 | -| **Keygen** | 15,600 | 0.039 | 25,641 || 0.026 | 38,462 | | ||

| 404 | -| **Signing (1 round)** | 26,600 | 0.067 | 15,038 || 0.044 | 22,556 | | ||

| 405 | -| **Signing (Ave)** | 106,400 | 0.266 | 3,759 || 0.177 | 5,639 | | ||

| 406 | -| **Verifying** | 18,800 | 0.047 | 21,277 || 0.031 | 31,915 | | ||

| 407 | - | ||

| 408 | - | ||

| 409 | - | ||

| 410 | -**NOTE:** Masking and shuffling countermeasures are integrated into the architecture and there is a work-in-progress to make it configureble to be enabled or disabled at synthesis time. | ||

| 411 | - | ||

| 412 | -The area overhead associated with enabling these countermeasures is as follows: | ||

| 413 | - | ||

| 414 | -|| Freq [MHz] | 400 ||| 600 || | ||

| 415 | -| --------------------- | ---------------- | ------------: | ---------------------- | --- | ------------: | ---------------------- | | ||

| 416 | -| **"Protected"** | **Latency [CC]** | **Time [ms]** | **Performance [IOPS]** || **Time [ms]** | **Performance [IOPS]** | | ||

| 417 | -| **keygen** | 15,600 | 0.039 | 25,641 || 0.026 | 38,462 | | ||

| 418 | -| **Signing (1 round)** | 36,700 | 0.092 | 10,899 || 0.061 | 16,349 | | ||

| 419 | -| **Signing (Ave)** | 146,800 | 0.367 | 2,725 || 0.245 | 4,087 | | ||

| 420 | -| **Verifying** | 18,800 | 0.047 | 21,277 || 0.031 | 31,915 | | ||

| 421 | - | ||

| 422 | - | ||

| 423 | - | ||

| 424 | - | ||

| 425 | -- CNSA 2.0 only allows the highest security level (Level-5) for PQC which is ML-DSA-87, and **Adams Bridge only supports ML-DSA-87 parameter set.** | ||

| 426 | -- The requried area for the unprotected ML-DSA-87 is 0.0366mm2 @5nm: | ||

| 427 | - - 0.0146mm2 for stdcell | ||

| 428 | - - 0.0220mm2 for ram area for 57.38 KB memory. | ||

| 429 | - | ||

| 430 | -- The requried area for the protected ML-DSA-87 is 0.114mm2 @5nm: | ||

| 431 | - - 0.0921mm2 for stdcell | ||

| 432 | - - 0.0220mm2 for ram area for 57.38 KB memory. | ||

| 433 | - | ||

| 434 | -- The design is converging today at 600MHz at low, med & high voltage corners. (We have noticed the design converging to 1 GHz on a latest process node.) | ||

| 435 | - | ||

| 436 | -### Memory requirement | ||

| 437 | - | ||

| 438 | -The following table shows the required memory instances for ML-DSA-87: | ||

| 42 | +The following table shows the required memory instances for Adam's Bridge: | ||

| 439 | 43 | ||

| 440 | 44 | | Instance | Depth | Data Width | Strobe Width | | |

| 441 | -| -------------------------------------------- | ----- | ---------- | ------------ | | ||

| 442 | -| mldsa_top.mldsa_ctrl_inst.mldsa_sk_ram_bank0 | 596 | 32 || | ||

| 443 | -| mldsa_top.mldsa_ctrl_inst.mldsa_sk_ram_bank1 | 596 | 32 || | ||

| 444 | -| mldsa_top.mldsa_w1_mem_inst | 512 | 4 || | ||

| 445 | -| mldsa_top.mldsa_ram_inst0_bank0 | 832 | 96 || | ||

| 446 | -| mldsa_top.mldsa_ram_inst0_bank1 | 832 | 96 || | ||

| 447 | -| mldsa_top.mldsa_ram_inst1 | 576 | 96 || | ||

| 448 | -| mldsa_top.mldsa_ram_inst2 | 1408 | 96 || | ||

| 449 | -| mldsa_top.mldsa_ram_inst3 | 128 | 96 || | ||

| 450 | -| mldsa_top.mldsa_ctrl_inst.mldsa_sig_z_ram | 224 | 160 | 8 | | ||

| 451 | -| mldsa_top.mldsa_ctrl_inst.mldsa_pubkey_ram | 64 | 320 | 8 | | ||

| 45 | +| -------------------- | ----- | ---------- | ------------ | | ||

| 46 | +| abr_sk_mem_bank0 | 596 | 32 || | ||

| 47 | +| abr_sk_mem_bank1 | 596 | 32 || | ||

| 48 | +| abr_w1_mem | 512 | 4 || | ||

| 49 | +| abr_mem_inst0_bank0 | 832 | 96 || | ||

| 50 | +| abr_mem_inst0_bank1 | 832 | 96 || | ||

| 51 | +| abr_mem_inst1 | 576 | 96 || | ||

| 52 | +| abr_mem_inst2 | 1472 | 96 || | ||

| 53 | +| abr_mem_inst3 | 64 | 384 || | ||

| 54 | +| abr_sig_z_mem | 224 | 160 | 8 | | ||

| 55 | +| abr_pk_mem | 64 | 320 | 8 | | ||

| 452 | 56 | ||

| 453 | 57 | ||

| 454 | 58 | All memories are modeled as 1 read 1 write port RAMs with a flopped read data. | |

| 455 | 59 | See abr_1r1w_ram.sv and abr_1r1w_be_ram.sv for examples. | |

| 60 | +Strobe width describes the number of bits enabled by each strobe. All strobed memories are byte enabled in the design. | ||

| 456 | 61 | ||

| 457 | -### Signing perofrmance | ||

| 62 | +# Zeroize | ||

| 458 | 63 | ||

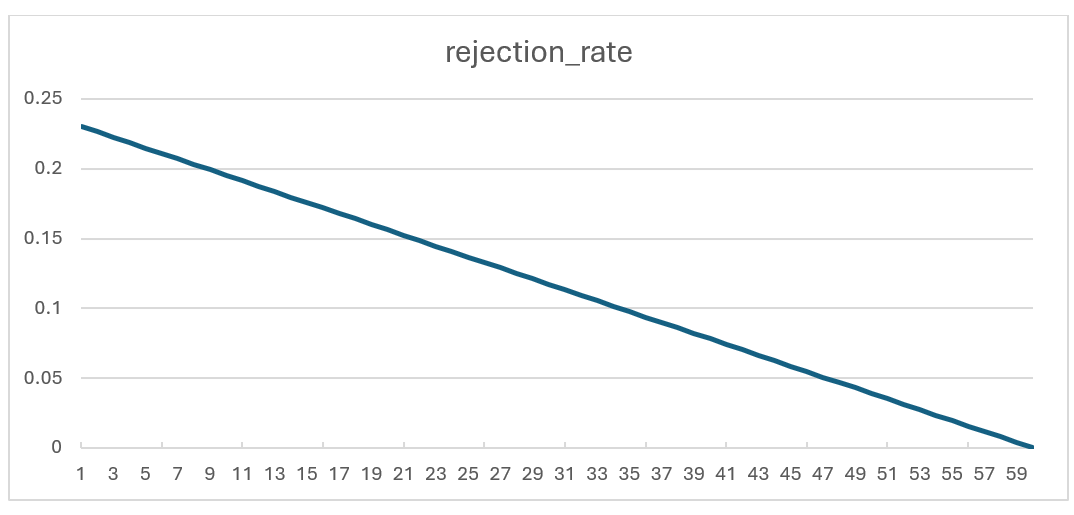

| 459 | -The signing operation is the most time-consuming part of the MLDSA algorithm. However, it is not constant-time due to the inherent nature of ML-DSA. The signing process involves a loop that continues until all validity checks are passed. The number of iterations depends on the provided privkey, message, and sign_rnd. | ||

| 64 | +The ZEROIZE bit in the control register clears all internal data-path registers that hold or have held secret-derived values. This prevents residual sensitive data from leaking through side-channel analysis or from being consumed by a subsequent operation. | ||

| 460 | 65 | ||

| 461 | -According to FIPS 204 recommendations, there is no mechanism to interrupt the signing loop. Nevertheless, for the ML-DSA-87 parameter set, the average number of required loops is 3.85. | ||

| 66 | +Firmware must issue zeroize: | ||

| 67 | +- After every completed operation, before starting the next command. | ||

| 68 | +- After any error or aborted operation, before re-issuing a command or reading results. | ||

| 462 | 69 | ||

| 463 | -# Proposed architecture | ||

| 70 | +Hardware behavior: | ||

| 71 | +- Zeroize takes the highest priority after reset. | ||

| 72 | +- The ZEROIZE control-register field is a pulse command: firmware writes a 1; the register auto-clears after one clock cycle. However, the hardware zeroize operation itself takes multiple cycles because on-chip SRAM is scrubbed one address per cycle. Firmware must poll the STATUS register and wait for ready before issuing the next command. | ||

| 73 | +- After zeroize completes, the STATUS register returns to ready, and the engine accepts a new command. | ||

| 464 | 74 | ||

| 465 | -The value of k and l is determined based on the security level of the system defined by NIST as follows: | ||

| 75 | +# Area Results | ||

| 466 | 76 | ||

| 467 | -| Algorithm Name | Security Level | k | l | | ||

| 468 | -| :------------- | :------------- | :-- | :-- | | ||

| 469 | -| ML-DSA-87 | Level-5 | 8 | 7 | | ||

| 77 | +- The required area for the protected Adams Bridge (ML-DSA-87 + ML-KEM-1024) is 0.1096mm2 @5nm: | ||

| 78 | + - 0.0860mm2 for stdcell | ||

| 79 | + - 0.0236mm2 for ram area. | ||

| 470 | 80 | ||

| 81 | +For per-algorithm performance breakdowns, see the Performance and Area Results sections in [AdamsBridge\_MLDSA.md](AdamsBridge_MLDSA.md) and [AdamsBridge\_MLKEM.md](AdamsBridge_MLKEM.md). | ||

| 471 | 82 | ||

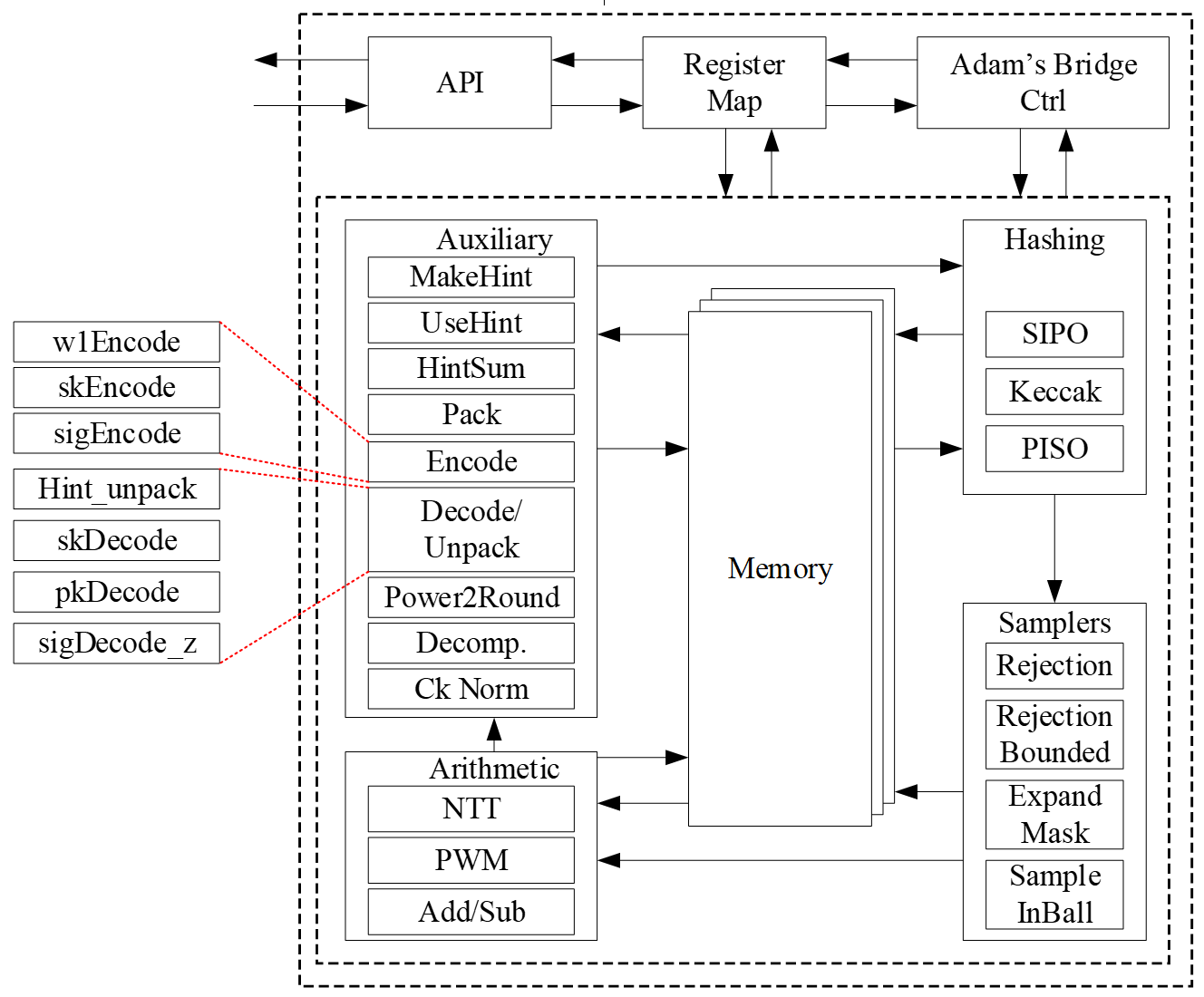

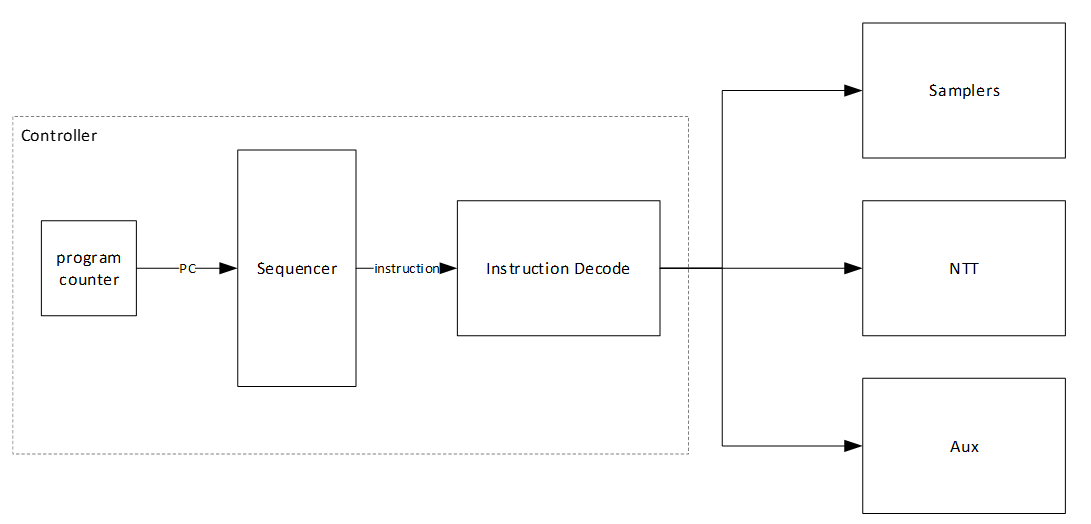

| 472 | -In the hardware design, using an instruction-set processor yields a smaller, simpler, and more controllable design. By fine-tuning hardware acceleration, we achieve efficiency without excessive logic overhead. We implement all computation blocks in hardware while maintaining flexibility for future extensions. This adaptability proves crucial in a rapidly evolving field like post-quantum cryptography (PQC), even amidst existing HW architectures. | ||

| 473 | - | ||

| 474 | -The Customized Instruction-Set Cryptography Engine is designed to provide efficient cryptographic operations while allowing flexibility for changes in NIST ML-DSA standards and varying security levels. This proposal outlines the architecture, instruction set design, sequencer functionality, and hardware considerations for the proposed architecture. This architecture is typically implemented as an Intellectual Property (IP) core within an FPGA or ASIC, featuring a pipelined design for streamlined execution and interfaces for seamless communication with the host processor. | ||

| 475 | - | ||

| 476 | -In our proposed architecture, we define specific instructions for various submodules, including SHAKE256, SHAKE128, NTT, INTT, etc. Each instruction is associated with an opcode and operands. By customizing these instructions, we can tailor the engine's behavior to different security levels. | ||

| 477 | - | ||

| 478 | -To execute the required instructions, a high-level controller acts as a sequencer, orchestrating a precise sequence of operations. Within the architecture, several memory blocks are accessible to submodules. However, it's the sequencer's responsibility to provide the necessary memory addresses for each operation. Additionally, the sequencer handles instruction fetching, decoding, operand retrieval, and overall data flow management. | ||

| 479 | - | ||

| 480 | -The high-level architecture of Adams Bridge controller is illustrated as follows: | ||

| 481 | - | ||

| 482 | - | ||

| 483 | - | ||

| 484 | -## Keccak architecture | ||

| 485 | - | ||

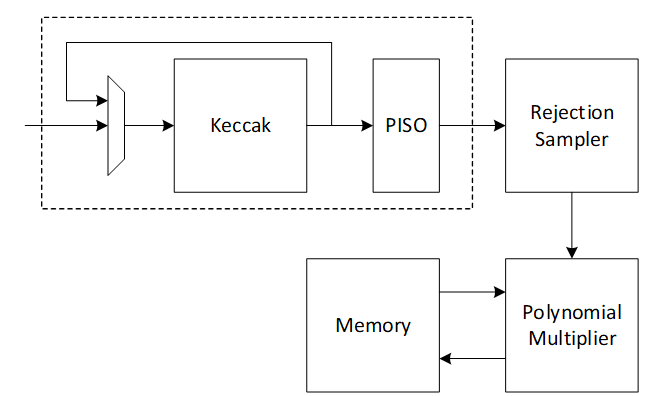

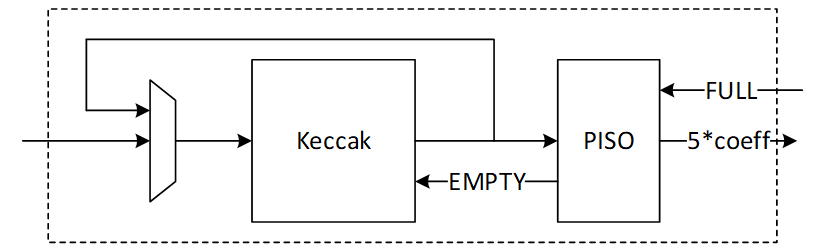

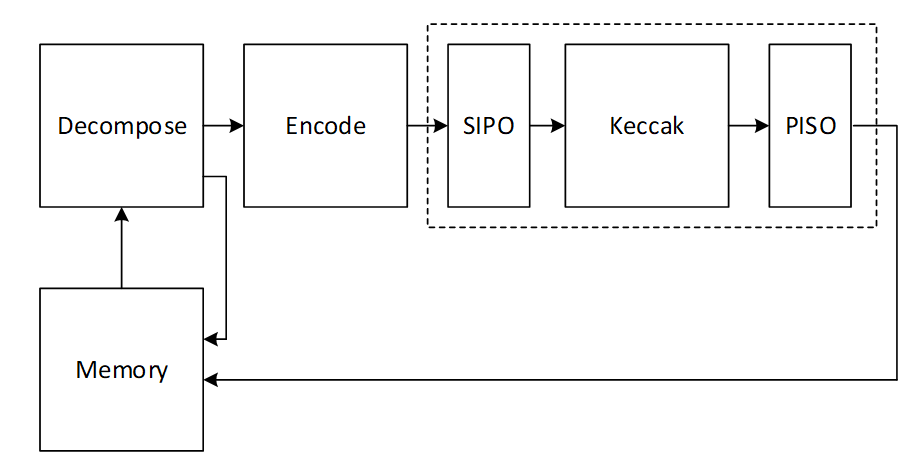

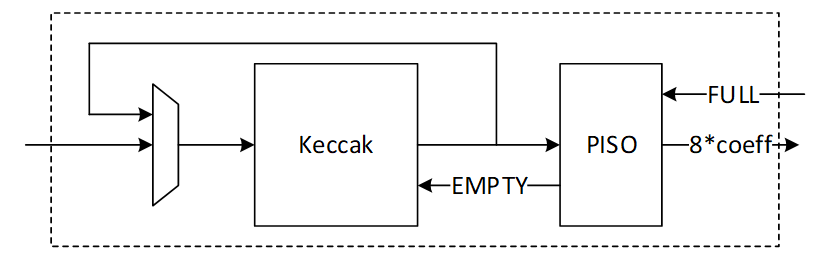

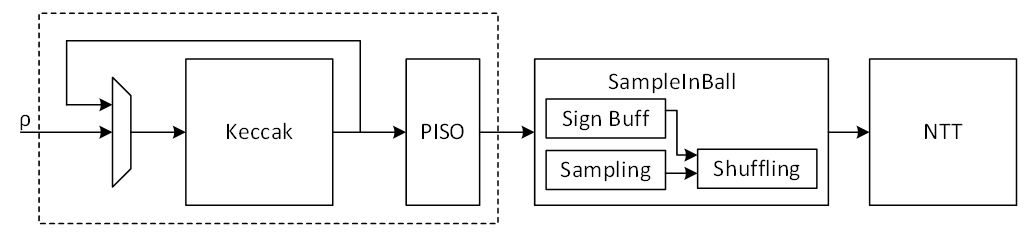

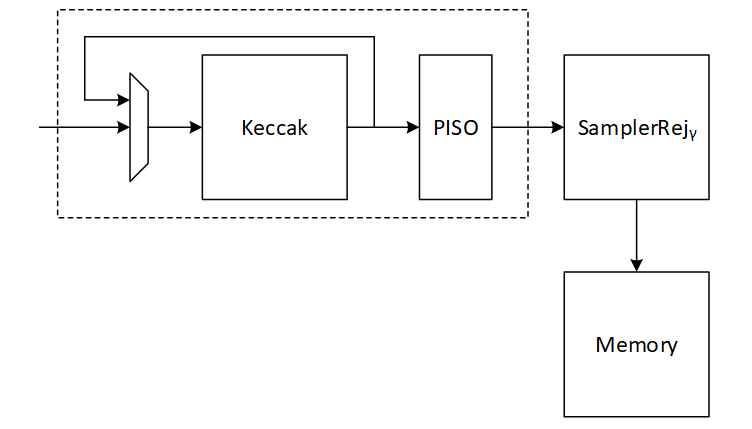

| 486 | -Hashing operation takes a significant portion of PQC latency. All samplers need to be fed by hashing functions. i.e., SHAKE128 and SHAKE256. Therefore, to improve the efficiency of the implementation, one should increase efficiency on the Keccak core, providing higher throughput using fewer hardware resources. Keccak core requires 24 rounds of the sponge function computation. We develop a dedicated SIPO (serial-in, parallel-out) and PISO (parallel-in, serial-out) for interfacing with this core in its input and output, respectively. | ||

| 487 | - | ||

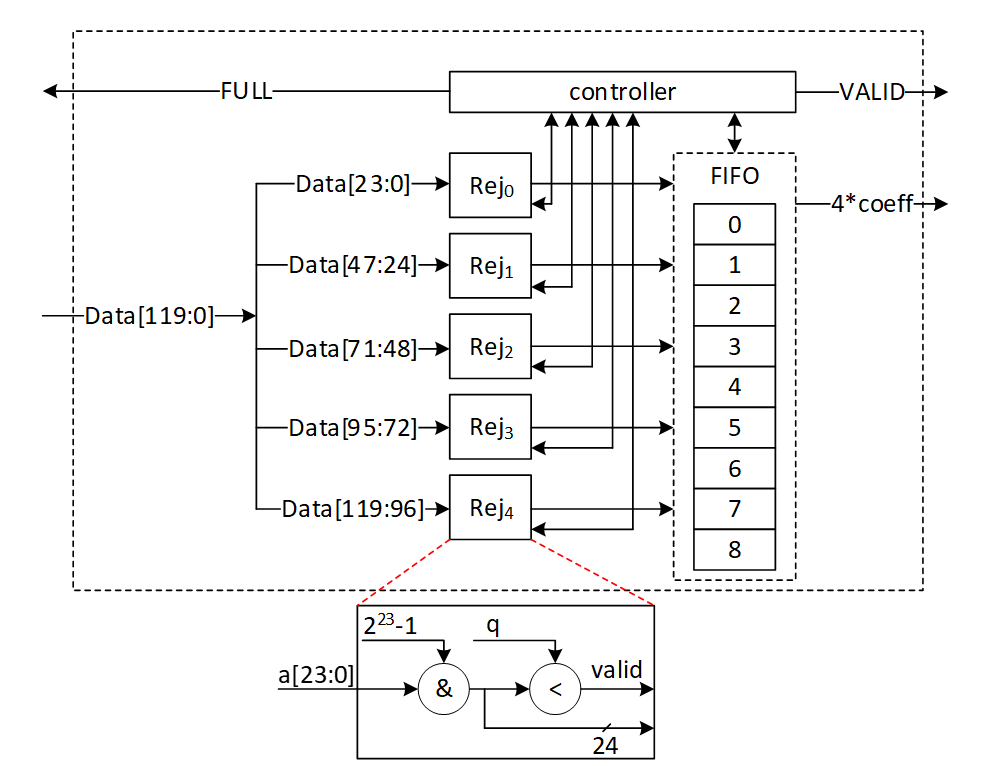

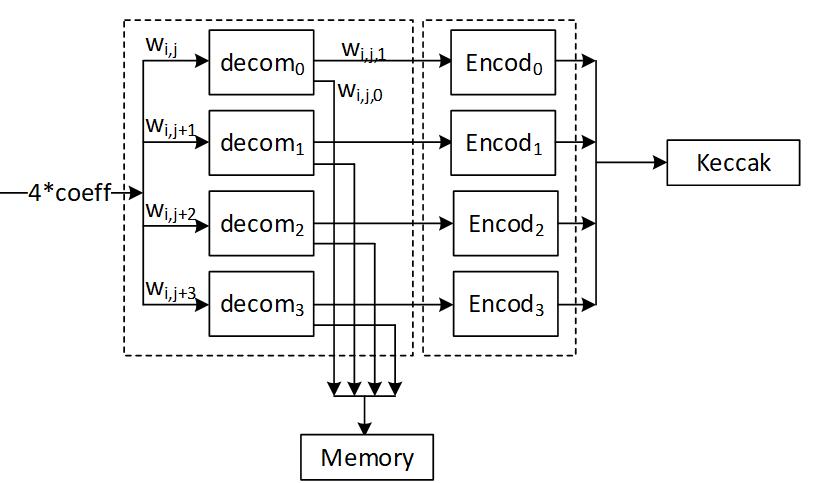

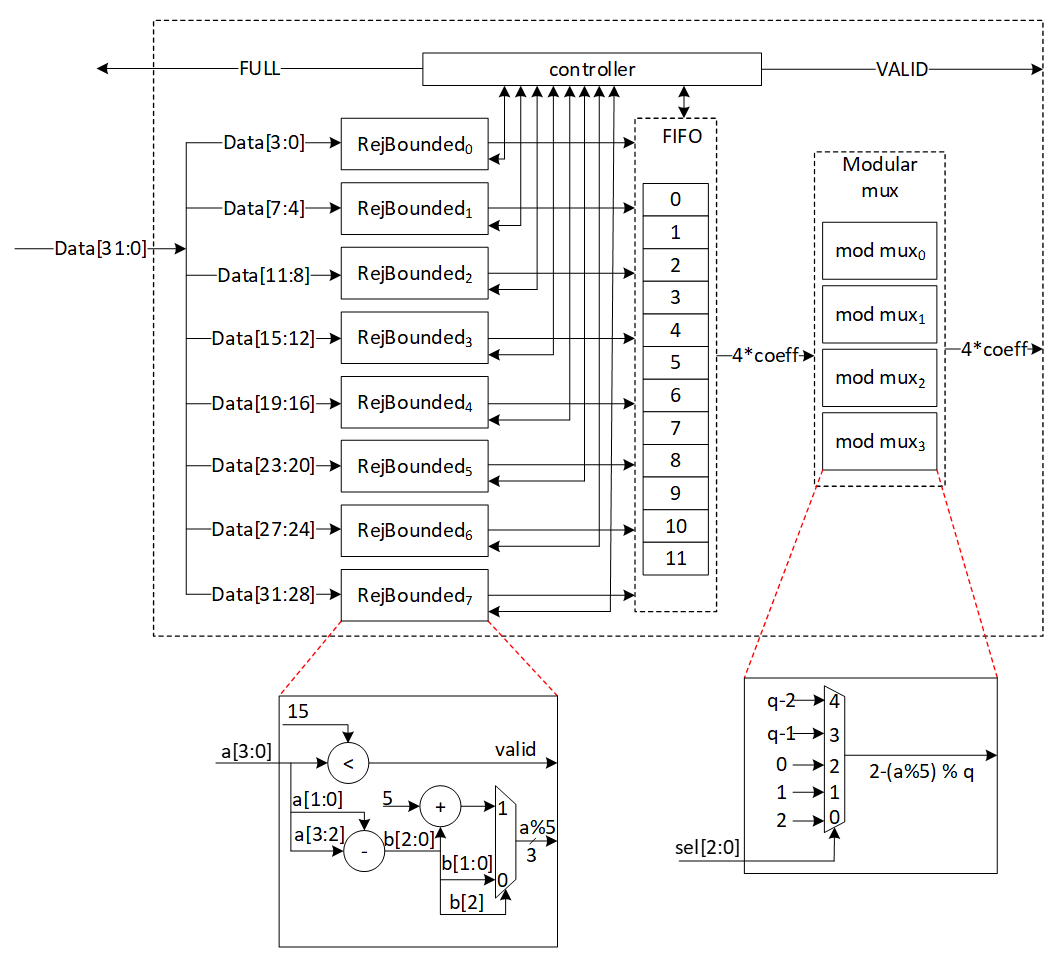

| 488 | -We propose an approach to design hardware rejection sampling architecture, which can offer more efficiency. This approach enables us to cascade the Keccak unit to rejection sampler and polynomial multiplication units that results in avoiding the memory access. | ||

| 489 | - | ||

| 490 | -In our optimized architecture, to reduce the failure probability due to the non-deterministic pattern of rejection sampling and avoid any stall cycle in polynomial multiplication, we use a FIFO to store sampled coefficients that match the speed of polynomial multiplication. The proposed sampler works in parallel with the Keccak core. Therefore, the latency for sampling unit is absorbed within the latency for a concurrently running Keccak core. | ||

| 491 | - | ||

| 492 | -In the input side, there are two different situations: | ||

| 493 | - | ||

| 494 | -1) The given block from SIPO is the last absorbing round. | ||

| 495 | - In this situation, the output PISO buffer should receive the Keccak state. | ||

| 496 | -2) The given block from SIPO is not the last absorbing round. | ||

| 497 | - In this situation, the output PISO buffer should not receive the Keccak state. However, the next input block from SIPO needs to be XORed with the Keccak state. | ||

| 498 | - | ||

| 499 | -There are two possible scenarios when the Keccak state has to be saved in the PISO buffer on the output side: | ||

| 500 | - | ||

| 501 | -1) PISO buffer EMPTY flag is not set. | ||

| 502 | - In this situation, Keccak should hold on and maintain the current state until EMPTY is activated and transfer the state into PISO buffer. | ||

| 503 | -2) PISO buffer EMPTY flag is set. | ||

| 504 | - In this situation, the state can be transferred to PISO buffer and the following round of Keccak (if any) can be started. | ||

| 505 | - | ||

| 506 | -### PISO Buffer | ||

| 507 | - | ||

| 508 | -The output of the Keccak unit is used to feed four different samplers at varying data rates. The Parallel in Serial out buffer is a generic buffer that can take the full width of the Keccak state and deliver it to the sampler units at the appropriate data rates. | ||

| 509 | - | ||

| 510 | -Input data from the Keccak can come at 1088 or 1344 bits per clock. During expand mask operation, the buffer needs to be written from a write pointer while valid data remains in the buffer. All other modes only require writing the full Keccak state into the buffer when it is empty. | ||

| 511 | - | ||

| 512 | -Output data rate varies \- 32 bits for RejBounded and SampleInBall, 80 bits for Expand Mask and 120 bits for SampleRejq. | ||

| 513 | - | ||

| 514 | -## Expand Mask architecture | ||

| 515 | - | ||

| 516 | -Dilithium samples the polynomials that make up the vectors and matrices independently, using a fixed seed value and a nonce value that increases the security as the input for Keccak. Keccak is used to take these seed and nonce and generate random stream bits. | ||

| 517 | - | ||

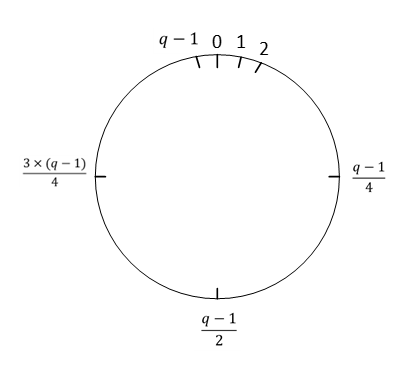

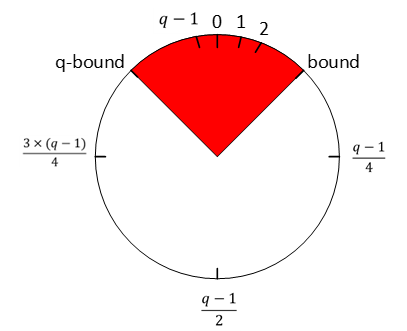

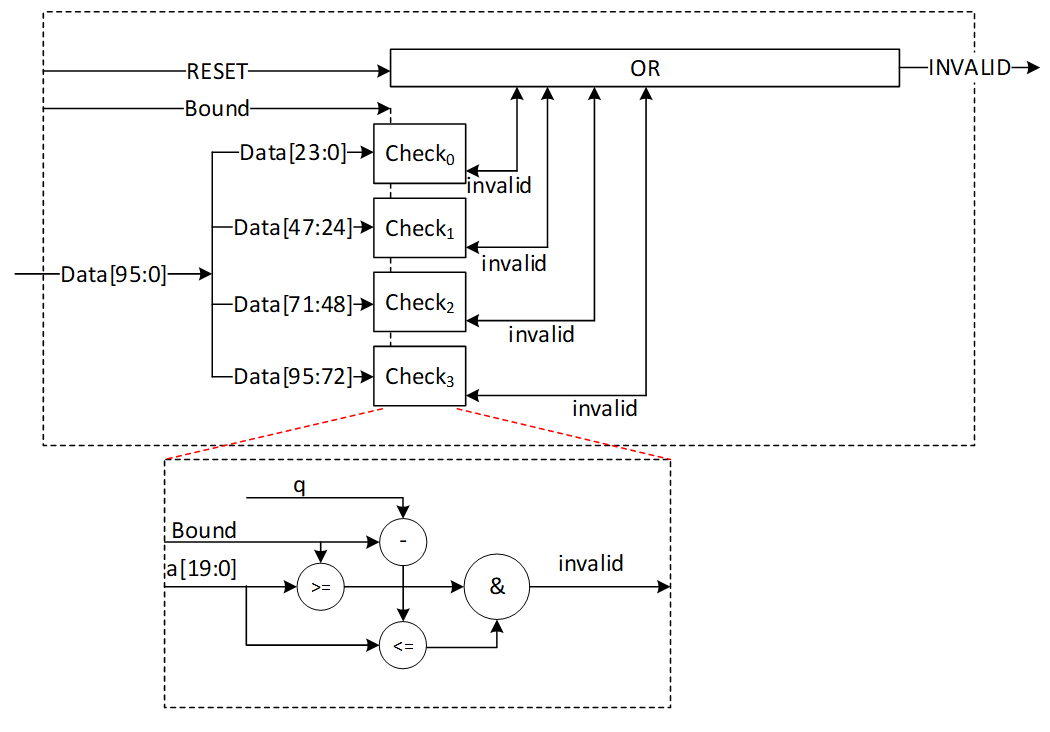

| 518 | -Expand Mask takes γ\-bits (20-bit for ML-DSA-87) and samples a vector such that all coefficients are in range of \[-γ\+1, γ\]. It continues to sample all required coefficients, n=256, for a polynomial. | ||

| 519 | - | ||

| 520 | -After sampling a polynomial with 256 coefficients, nonce will be changed and a new random stream will be generated using Keccak core and will be sampled by expand mask unit. | ||

| 521 | - | ||

| 522 | -The output of this operation results in a l different polynomial while each polynomial includes 256 coefficients. | ||

| 523 | - | ||

| 524 | -y1,0 y1,l-1 | ||

| 525 | - | ||

| 526 | -Expand Mask is used in signing operation of Dilithium. The output of expand mask sampler is stored into memory and will be used as an input for NTT module. | ||

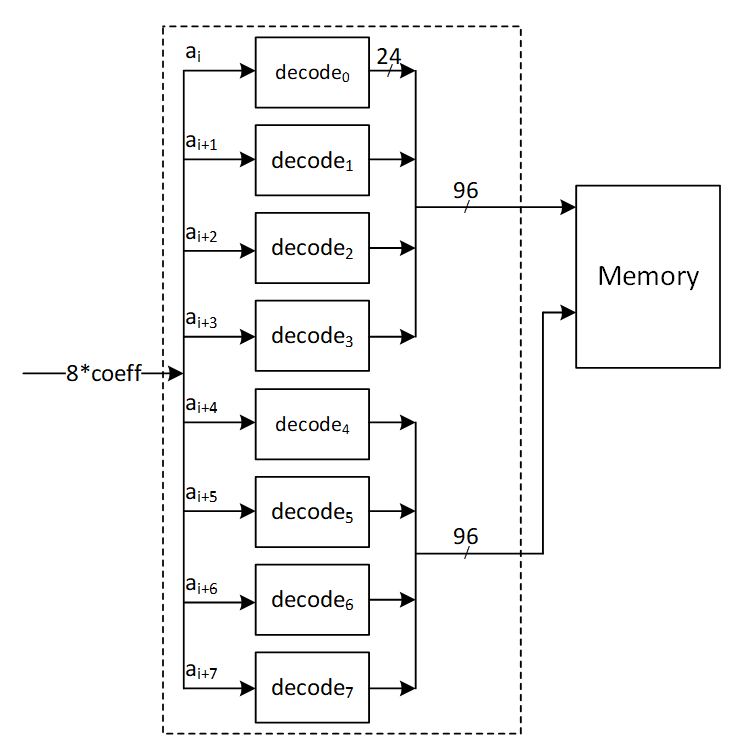

| 527 | - | ||

| 528 | -We propose an architecture to remove the cost of memory access since NTT needs input in a specific format, i.e., 4 coefficients per each memory address. To achieve this, we need to have a balanced throughput between all these modules to avoid large buffering or conflict between them. | ||

| 529 | - | ||

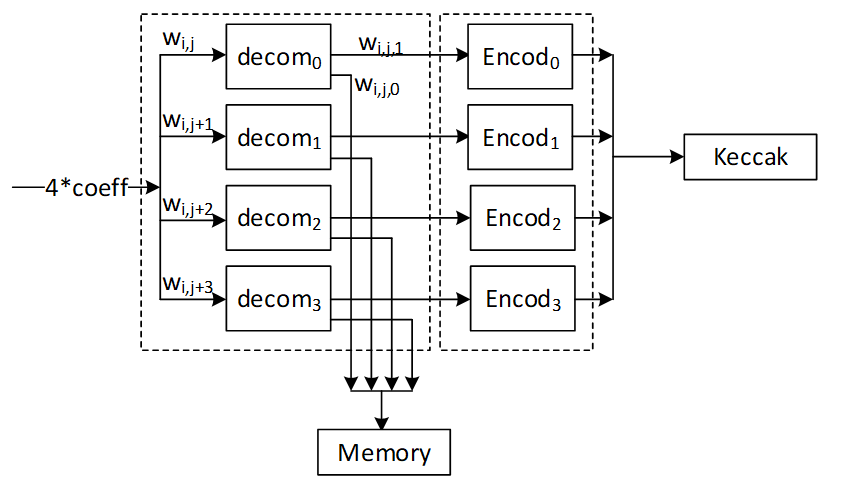

| 530 | -High-level architecture is illustrated as follows: | ||

| 531 | - | ||

| 532 | - | ||

| 533 | - | ||

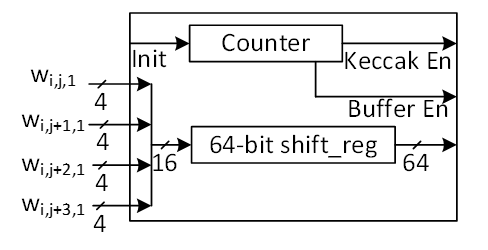

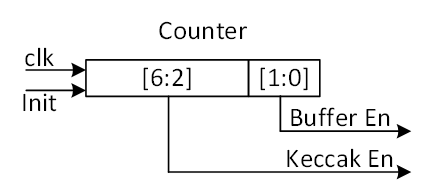

| 534 | -### Keccak interface to Expand Mask | ||

| 535 | - | ||

| 536 | -Keccak is used in SHAKE-256 configuration for expand mask operation. Hence, it will take the input data and generate 1088-bit output after each round. We propose implementing of Keccak while each round takes 12 cycles. The format of input data is as follows: | ||

| 537 | - | ||

| 538 | -Input data \= ρ' | n | ||

| 539 | - | ||

| 540 | -Where ρ' is seed with 512-bits, n=κ+r is the 16-bit nonce that will be incremented for each polynomial (r++) or if the signature is rejected by validity checks (\++). | ||

| 541 | - | ||

| 542 | -Since each bits (20-bit in for ML-DSA-87) is used for one coefficient, 256\*20=5120 bits are required for one polynomial which needs 5 rounds (5120/1088=4.7) of Keccak. | ||

| 543 | - | ||

| 544 | -To sample l polynomial (l=7 for ML-DSA-87), we need a total of 5\*7 \= 35 rounds of Keccak. | ||

| 545 | - | ||

| 546 | -There are two paths for Keccak input. While the input can be set by controller for new nonce in the case of next polynomial or rejected signature, the loop path is used to rerun Keccak for completing the current sampling process with l polynomial. | ||

| 547 | - | ||

| 548 | -Expand mask cannot take all 1088-bit output parallelly since it makes hardware architecture too costly and complex, and also there is no other input from Keccak for the next 12 cycles. Therefore, we propose a parallel-input serial-output (PISO) unit in between to store the Keccak output and feed rejection unit sequentially. | ||

| 549 | - | ||

| 550 | -### Expand Mask | ||

| 551 | - | ||

| 552 | -This unit takes data from the output of SHAKE-256 stored in a PISO buffer. The required cycles for this unit is 4.7 rounds of Keccak for one polynomial and 35 rounds of Keccak for all required polynomial (l polynomial which l=7 for ML-DSA-87). | ||

| 553 | - | ||

| 554 | -In our optimized architecture, this unit works in parallel with the Keccak core. Therefore, the latency for expand mask is absorbed within the latency for a concurrently running Keccak core. | ||

| 555 | - | ||

| 556 | -Our proposed NTT unit takes four coefficients per cycle from one memory address. It helps to avoid memory access challenges and make the control logic too complicated. This implies that the optimal speed of the expand mask module is to sample four coefficients per cycle. | ||

| 557 | - | ||

| 558 | -There are 4 rejection sampler circuits corresponding to each 20-bit input. The total coefficient after each round of Keccak is 1088/20 \= 54.4 coefficients. We keep expand mask unit working in all cycles and generating 4 coefficients per cycle without any interrupt. That means 12\*4=48 coefficients can be processed during each Keccak round. | ||

| 559 | - | ||

| 560 | - | ||

| 561 | - | ||

| 562 | -After 12 cycles, 48 coefficients are processed by the expand mask unit, and there are still 128-bit inside PISO. To maximize the utilization factor of our hardware resources, Keccak core will check the PISO status. If PISO contains 4 coefficients or more (the required inputs for expand mask unit), EMPTY flag will not be set, and Keccak will wait until the next cycle. Hence, expand mask unit takes 13 cycles to process 52 coefficients, and the last 48-bit will be combined with the next Keccak round to be processed. | ||

| 563 | - | ||

| 564 | - | ||

| 565 | - | ||

| 566 | -### Performance of Expand Mask | ||

| 567 | - | ||

| 568 | -Sampling a polynomial with 256 coefficients takes 256/4=64 cycles. The first round of Keccak needs 12 cycles, and the rest of Keccak operation will be parallel with expand mask operation. | ||

| 569 | - | ||

| 570 | -For a complete expand mask for Dilithium ML-DSA-87 with 7 polynomials, 7\*64+12=460 cycles are required using sequential operation. However, our design can be duplicated to enable parallel sampling for two different polynomials. Having two parallel design results in 268 cycles, while three parallel design results in 204 cycles at the cost of more resource utilization. | ||

| 571 | - | ||

| 572 | -## NTT architecture | ||

| 573 | - | ||

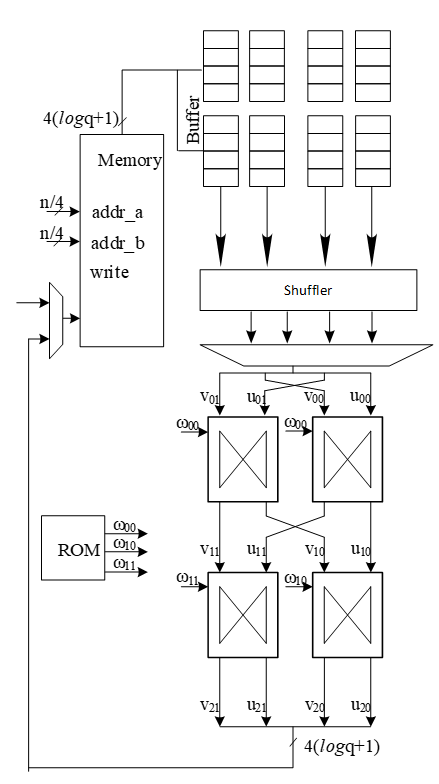

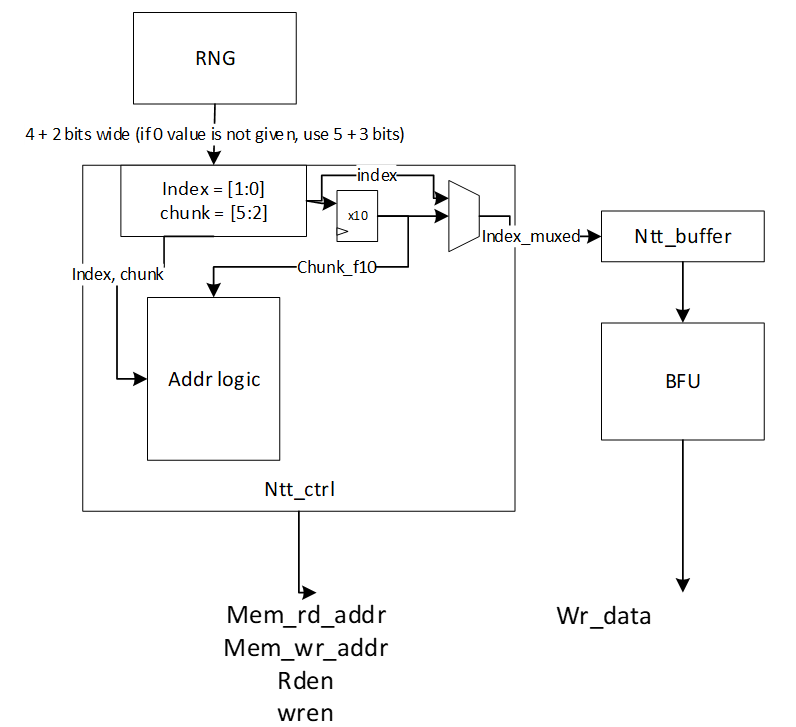

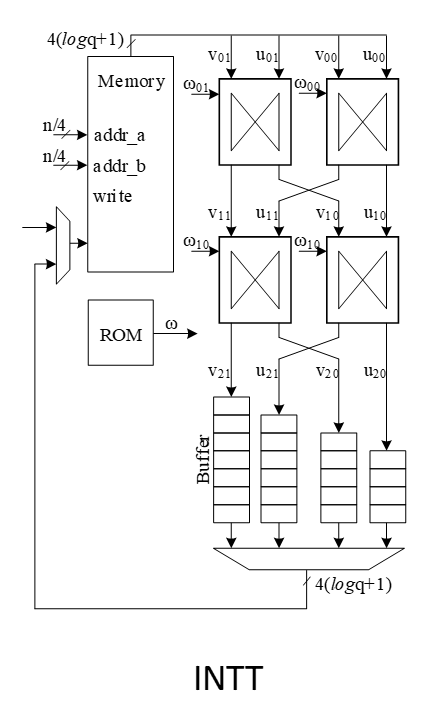

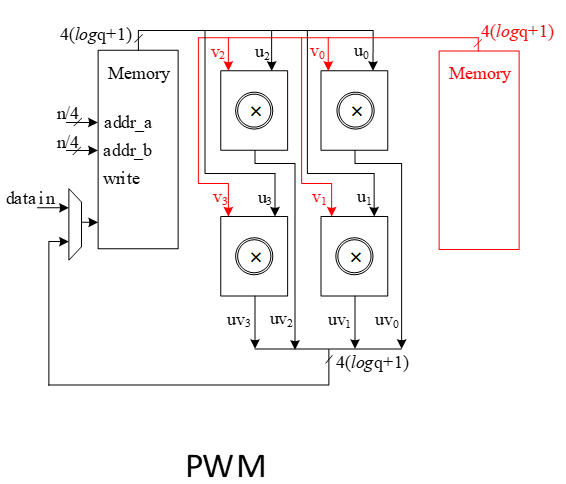

| 574 | -The most computationally intensive operation in lattice-based PQC schemes is polynomial multiplication which can be accelerated using NTT. However, NTT is still a performance bottleneck in lattice-based cryptography. We propose improved NTT architecture with highly efficient modular reduction. This architecture supports NTT, INTT, and point-wise multiplication (PWM) to enhance the design from resource sharing point-of-view while reducing the pre-processing cost of NTT and post-processing cost of INTT. | ||

| 575 | - | ||

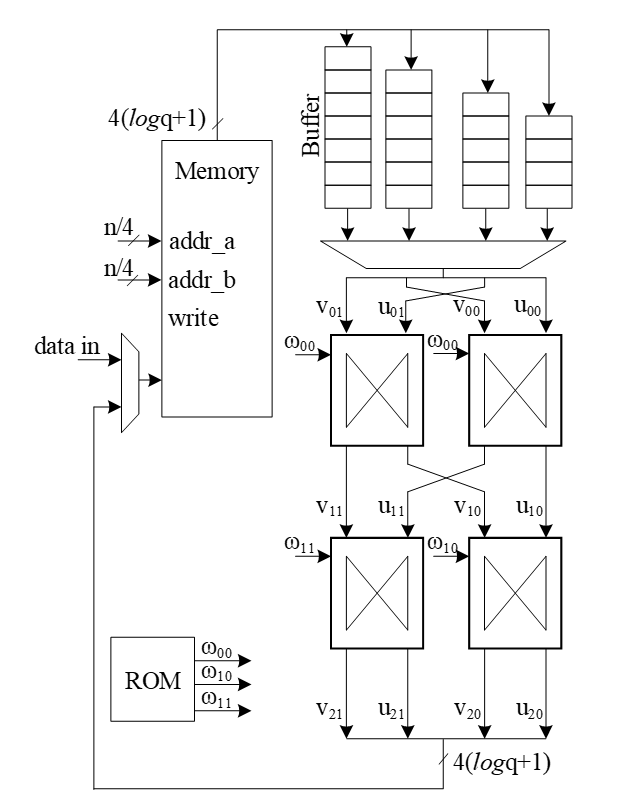

| 576 | -Our NTT architecture exploits a merged-layer NTT technique using two pipelined stages with two parallel cores in each stage level, making 4 butterfly cores in total. Our proposed parallel pipelined butterfly cores enable us to perform Radix-4 NTT/INTT operation with 4 parallel coefficients. While memory bandwidth limits the efficiency of the butterfly operation, we use a specific memory pattern to store four coefficients per address. | ||

| 577 | - | ||

| 578 | -An NTT operation can be regarded as an iterative operation by applying a sequence of butterfly operations on the input polynomial coefficients. A butterfly operation is an arithmetic operation that combines two coefficients to obtain two outputs. By repeating this process for different pairs of coefficients, the NTT operation can be computed in a logarithmic number of steps. | ||

| 579 | - | ||

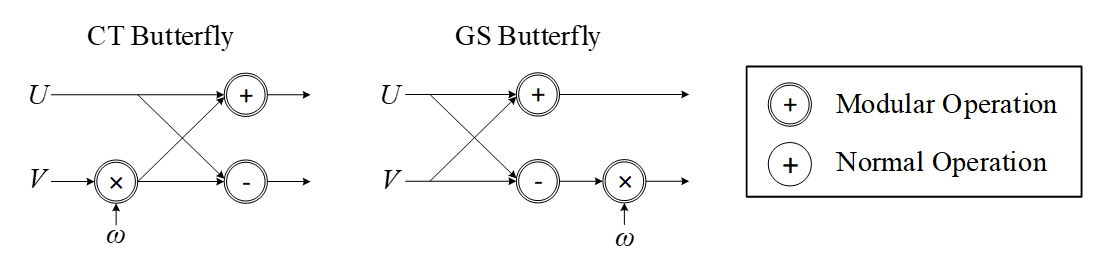

| 580 | -Cooley-Tukey (CT) and Gentleman-Sande (GS) butterfly configurations can be used to facilitate NTT/INTT computation. The bit-reverse function reverses the bits of the coefficient index. However, the bit-reverse permutation can be skipped by using CT butterfly for NTT and GS for INTT. | ||

| 581 | - | ||

| 582 | - | ||

| 583 | - | ||

| 584 | -We propose a merged NTT architecture using dual radix-4 design by employing four pipelined stages with two parallel cores at each stage level. | ||

| 585 | - | ||

| 586 | -The following presents the high-level architecture of our proposed NTT to take advantage of Merged architectural design: | ||

| 587 | - | ||

| 588 | - | ||

| 589 | - | ||

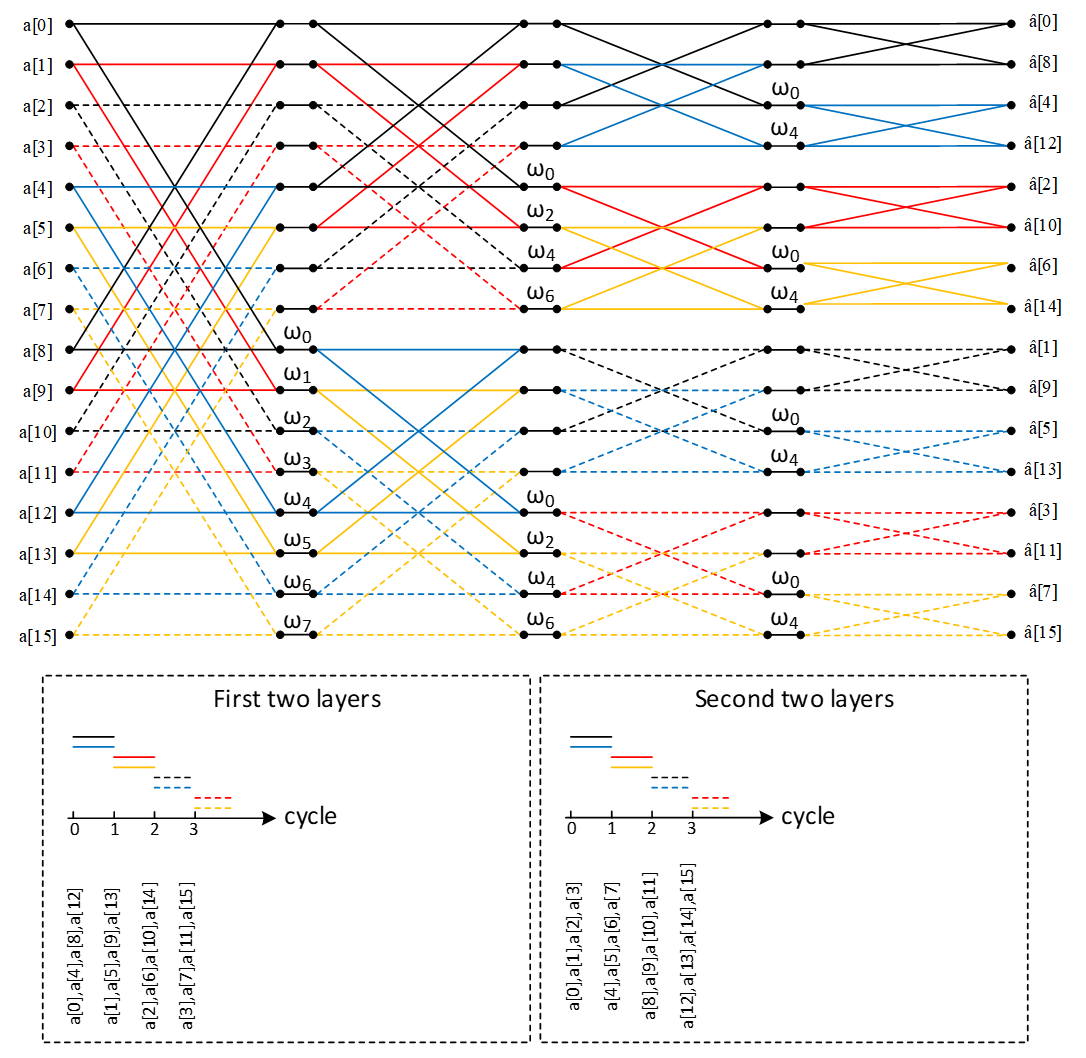

| 590 | -The following figure illustrates a 16-point NTT data flow based on our proposed architecture: | ||

| 591 | - | ||

| 592 | - | ||

| 593 | - | ||

| 594 | -A merged-layer NTT technique uses two pipelined stages with two parallel cores in each stage level, making 4 butterfly cores in total. The parallel pipelined butterfly cores enable us to perform Radix-4 NTT/INTT operation with 4 parallel coefficients. | ||

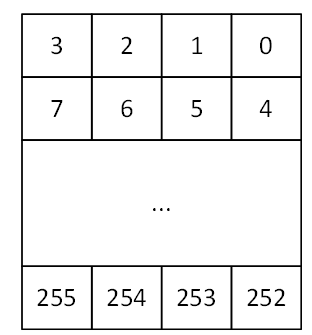

| 595 | - | ||

| 596 | -However, NTT requires a specific memory pattern that may limit the efficiency of the butterfly operation. For Dilithium use case, there are n=256 coefficients per polynomial that requires log n=8 layers of NTT operations. Each butterfly unit takes two coefficients while difference between the indexes is 28-i in ith stage. That means for the first stage, the given indexes for each butterfly unit are (k, k+128): | ||

| 597 | - | ||

| 598 | -Stage 1 input indexes: {(0, 128), {1, 129), (2, 130), …, (127, 255)} | ||

| 599 | - | ||

| 600 | -Stage 2 input indexes: {(0, 64), {1, 65), (2, 66), …, (63, 127), (128, 192), (129, 193), …, (191, 255)} | ||

| 601 | - | ||

| 602 | -… | ||

| 603 | - | ||

| 604 | -Stage 8 input indexes: {(0, 1), {2, 3), (4, 5), …, (254, 255)} | ||

| 605 | - | ||

| 606 | -There are several considerations for that: | ||

| 607 | - | ||

| 608 | -- We need access to 4 coefficients per cycle to match the throughput into 2×2 butterfly units. | ||

| 609 | -- An optimized architecture provides a memory with only one reading port, and one writing port. | ||

| 610 | -- Based on the previous two notes, each memory address contains 4 coefficients. | ||

| 611 | -- The initial coefficients are produced sequentially by Keccak and samplers. Specifically, they begin with 0 and continue incrementally up to 255\. Hence, at the very beginning cycle, the memory contains (0, 1, 2, 3\) in the first address, (4, 5, 6, 7\) in second address, and so on. | ||

| 612 | -- The cost of in-place memory relocation to align the memory content is not negligible. Particularly, it needs to be repeated for each stage. | ||

| 613 | - | ||

| 614 | -While memory bandwidth limits the efficiency of the butterfly operation, we use a specific memory pattern to store four coefficients per address. | ||

| 615 | - | ||

| 616 | -We propose a pipeline architecture the read memory in a particular pattern and using a set of buffers, the corresponding coefficients are fed into NTT block. | ||

| 617 | - | ||

| 618 | -The initial memory contains the indexes as follows: | ||

| 619 | - | ||

| 620 | -| Address | Initial Memory Content |||| | ||

| 621 | -| ------- | ---------------------- | --- | --- | --- | | ||

| 622 | -|||||| | ||

| 623 | -| 0 | 0 | 1 | 2 | 3 | | ||

| 624 | -| 1 | 4 | 5 | 6 | 7 | | ||

| 625 | -| 2 | 8 | 9 | 10 | 11 | | ||

| 626 | -| 3 | 12 | 13 | 14 | 15 | | ||

| 627 | -| 4 | 16 | 17 | 18 | 19 | | ||

| 628 | -| 5 | 20 | 21 | 22 | 23 | | ||

| 629 | -| 6 | 24 | 25 | 26 | 27 | | ||

| 630 | -| 7 | 28 | 29 | 30 | 31 | | ||

| 631 | -| 8 | 32 | 33 | 34 | 35 | | ||

| 632 | -| 9 | 36 | 37 | 38 | 39 | | ||

| 633 | -| 10 | 40 | 41 | 42 | 43 | | ||

| 634 | -| 11 | 44 | 45 | 46 | 47 | | ||

| 635 | -| 12 | 48 | 49 | 50 | 51 | | ||

| 636 | -| 13 | 52 | 53 | 54 | 55 | | ||

| 637 | -| 14 | 56 | 57 | 58 | 59 | | ||

| 638 | -| 15 | 60 | 61 | 62 | 63 | | ||

| 639 | -| 16 | 64 | 65 | 66 | 67 | | ||

| 640 | -| 17 | 68 | 69 | 70 | 71 | | ||

| 641 | -| 18 | 72 | 73 | 74 | 75 | | ||

| 642 | -| 19 | 76 | 77 | 78 | 79 | | ||

| 643 | -| 20 | 80 | 81 | 82 | 83 | | ||

| 644 | -| 21 | 84 | 85 | 86 | 87 | | ||

| 645 | -| 22 | 88 | 89 | 90 | 91 | | ||

| 646 | -| 23 | 92 | 93 | 94 | 95 | | ||

| 647 | -| 24 | 96 | 97 | 98 | 99 | | ||

| 648 | -| 25 | 100 | 101 | 102 | 103 | | ||

| 649 | -| 26 | 104 | 105 | 106 | 107 | | ||

| 650 | -| 27 | 108 | 109 | 110 | 111 | | ||

| 651 | -| 28 | 112 | 113 | 114 | 115 | | ||

| 652 | -| 29 | 116 | 117 | 118 | 119 | | ||

| 653 | -| 30 | 120 | 121 | 122 | 123 | | ||

| 654 | -| 31 | 124 | 125 | 126 | 127 | | ||

| 655 | -| 32 | 128 | 129 | 130 | 131 | | ||

| 656 | -| 33 | 132 | 133 | 134 | 135 | | ||

| 657 | -| 34 | 136 | 137 | 138 | 139 | | ||

| 658 | -| 35 | 140 | 141 | 142 | 143 | | ||

| 659 | -| 36 | 144 | 145 | 146 | 147 | | ||

| 660 | -| 37 | 148 | 149 | 150 | 151 | | ||

| 661 | -| 38 | 152 | 153 | 154 | 155 | | ||

| 662 | -| 39 | 156 | 157 | 158 | 159 | | ||

| 663 | -| 40 | 160 | 161 | 162 | 163 | | ||

| 664 | -| 41 | 164 | 165 | 166 | 167 | | ||

| 665 | -| 42 | 168 | 169 | 170 | 171 | | ||

| 666 | -| 43 | 172 | 173 | 174 | 175 | | ||

| 667 | -| 44 | 176 | 177 | 178 | 179 | | ||

| 668 | -| 45 | 180 | 181 | 182 | 183 | | ||

| 669 | -| 46 | 184 | 185 | 186 | 187 | | ||

| 670 | -| 47 | 188 | 189 | 190 | 191 | | ||

| 671 | -| 48 | 192 | 193 | 194 | 195 | | ||

| 672 | -| 49 | 196 | 197 | 198 | 199 | | ||

| 673 | -| 50 | 200 | 201 | 202 | 203 | | ||

| 674 | -| 51 | 204 | 205 | 206 | 207 | | ||

| 675 | -| 52 | 208 | 209 | 210 | 211 | | ||

| 676 | -| 53 | 212 | 213 | 214 | 215 | | ||

| 677 | -| 54 | 216 | 217 | 218 | 219 | | ||

| 678 | -| 55 | 220 | 221 | 222 | 223 | | ||

| 679 | -| 56 | 224 | 225 | 226 | 227 | | ||

| 680 | -| 57 | 228 | 229 | 230 | 231 | | ||

| 681 | -| 58 | 232 | 233 | 234 | 235 | | ||

| 682 | -| 59 | 236 | 237 | 238 | 239 | | ||

| 683 | -| 60 | 240 | 241 | 242 | 243 | | ||

| 684 | -| 61 | 244 | 245 | 246 | 247 | | ||

| 685 | -| 62 | 248 | 249 | 250 | 251 | | ||

| 686 | -| 63 | 252 | 253 | 254 | 255 | | ||

| 687 | - | ||

| 688 | - | ||

| 689 | -Suppose memory is read in this pattern: | ||

| 690 | - | ||

| 691 | -Addr: 0, 16, 32, 48, 1, 17, 33, 49, …, 15, 31, 47, 63 | ||

| 692 | - | ||

| 693 | -The input goes to the customized buffer architecture as follows: | ||

| 694 | - | ||

| 695 | -| 0 | → |||||||| | ||

| 696 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 697 | -| 1 ||||||||| | ||

| 698 | -| 2 ||||||||| | ||

| 699 | -| 3 ||||||||| | ||

| 700 | - | ||

| 701 | - | ||

| 702 | -Cycle 0 reading address 0 | ||

| 703 | - | ||

| 704 | -| 64 | → |||| 0 |||| | ||

| 705 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 706 | -| 65 |||| 1 ||||| | ||

| 707 | -| 66 ||| 2 |||||| | ||

| 708 | -| 67 || 3 ||||||| | ||

| 709 | - | ||

| 710 | - | ||

| 711 | -Cycle 1 reading address 16 | ||

| 712 | - | ||

| 713 | -| 128 | → |||| 64 | 0 ||| | ||

| 714 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 715 | -| 129 |||| 65 | 1 |||| | ||

| 716 | -| 130 ||| 66 | 2 ||||| | ||

| 717 | -| 131 || 67 | 3 |||||| | ||

| 718 | - | ||

| 719 | - | ||

| 720 | -Cycle 2 reading address 32 | ||

| 721 | - | ||

| 722 | -| 192 | → |||| 128 | 64 | 0 || | ||

| 723 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 724 | -| 193 |||| 129 | 65 | 1 ||| | ||

| 725 | -| 194 ||| 130 | 66 | 2 |||| | ||

| 726 | -| 195 || 131 | 67 | 3 ||||| | ||

| 727 | - | ||

| 728 | - | ||

| 729 | -Cycle 3 reading address 48 | ||

| 730 | - | ||

| 731 | -| 4 | → |||| 192 | 128 | 64 | 0 | | ||

| 732 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 733 | -| 5 |||| 193 | 129 | 65 | 1 || | ||

| 734 | -| 6 ||| 194 | 130 | 66 | 2 ||| | ||

| 735 | -| 7 || 195 | 131 | 67 | 3 |||| | ||

| 736 | - | ||

| 737 | - | ||

| 738 | -Cycle 4 reading address 1 | ||

| 739 | - | ||

| 740 | -| 68 | → |||| 4 | 192 | 128 | 64 | | ||

| 741 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 742 | -| 69 |||| 5 | 193 | 129 | 65 | 1 | | ||

| 743 | -| 70 ||| 6 | 194 | 130 | 66 | 2 || | ||

| 744 | -| 71 || 7 | 195 | 131 | 67 | 3 ||| | ||

| 745 | - | ||

| 746 | - | ||

| 747 | -Cycle 5 reading address 17 | ||

| 748 | - | ||

| 749 | -The highlighted value in the first buffer contains the required coefficients for our butterfly units, i.e., (0, 128\) and (64, 192). Since we merged the 1 and second layers of NTT stages, the output of the first parallel butterfly units need to exchange one coefficient and then the required input for the second parallel set of butterfly units is ready, i.e., (0, 64\) and (128, 192). | ||

| 750 | - | ||

| 751 | -After completing the first round of operation including NTT stage 1 and 2, the memory contains the following data: | ||

| 752 | - | ||

| 753 | -| Address | Memory Content after 1&2 stages |||| | ||

| 754 | -| ------- | ------------------------------- | --- | --- | --- | | ||

| 755 | -|||||| | ||

| 756 | -| 0 | 0 | 64 | 128 | 192 | | ||

| 757 | -| 1 | 1 | 65 | 129 | 193 | | ||

| 758 | -| 2 | 2 | 66 | 130 | 194 | | ||

| 759 | -| 3 | 3 | 67 | 131 | 195 | | ||

| 760 | -| 4 | 4 | 68 | 132 | 196 | | ||

| 761 | -| 5 | 5 | 69 | 133 | 197 | | ||

| 762 | -| 6 | 6 | 70 | 134 | 198 | | ||

| 763 | -| 7 | 7 | 71 | 135 | 199 | | ||

| 764 | -| 8 | 8 | 72 | 136 | 200 | | ||

| 765 | -| 9 | 9 | 73 | 137 | 201 | | ||

| 766 | -| 10 | 10 | 74 | 138 | 202 | | ||

| 767 | -| 11 | 11 | 75 | 139 | 203 | | ||

| 768 | -| 12 | 12 | 76 | 140 | 204 | | ||

| 769 | -| 13 | 13 | 77 | 141 | 205 | | ||

| 770 | -| 14 | 14 | 78 | 142 | 206 | | ||

| 771 | -| 15 | 15 | 79 | 143 | 207 | | ||

| 772 | -| 16 | 16 | 80 | 144 | 208 | | ||

| 773 | -| 17 | 17 | 81 | 145 | 209 | | ||

| 774 | -| 18 | 18 | 82 | 146 | 210 | | ||

| 775 | -| 19 | 19 | 83 | 147 | 211 | | ||

| 776 | -| 20 | 20 | 84 | 148 | 212 | | ||

| 777 | -| 21 | 21 | 85 | 149 | 213 | | ||

| 778 | -| 22 | 22 | 86 | 150 | 214 | | ||

| 779 | -| 23 | 23 | 87 | 151 | 215 | | ||

| 780 | -| 24 | 24 | 88 | 152 | 216 | | ||

| 781 | -| 25 | 25 | 89 | 153 | 217 | | ||

| 782 | -| 26 | 26 | 90 | 154 | 218 | | ||

| 783 | -| 27 | 27 | 91 | 155 | 219 | | ||

| 784 | -| 28 | 28 | 92 | 156 | 220 | | ||

| 785 | -| 29 | 29 | 93 | 157 | 221 | | ||

| 786 | -| 30 | 30 | 94 | 158 | 222 | | ||

| 787 | -| 31 | 31 | 95 | 159 | 223 | | ||

| 788 | -| 32 | 32 | 96 | 160 | 224 | | ||

| 789 | -| 33 | 33 | 97 | 161 | 225 | | ||

| 790 | -| 34 | 34 | 98 | 162 | 226 | | ||

| 791 | -| 35 | 35 | 99 | 163 | 227 | | ||

| 792 | -| 36 | 36 | 100 | 164 | 228 | | ||

| 793 | -| 37 | 37 | 101 | 165 | 229 | | ||

| 794 | -| 38 | 38 | 102 | 166 | 230 | | ||

| 795 | -| 39 | 39 | 103 | 167 | 231 | | ||

| 796 | -| 40 | 40 | 104 | 168 | 232 | | ||

| 797 | -| 41 | 41 | 105 | 169 | 233 | | ||

| 798 | -| 42 | 42 | 106 | 170 | 234 | | ||

| 799 | -| 43 | 43 | 107 | 171 | 235 | | ||

| 800 | -| 44 | 44 | 108 | 172 | 236 | | ||

| 801 | -| 45 | 45 | 109 | 173 | 237 | | ||

| 802 | -| 46 | 46 | 110 | 174 | 238 | | ||

| 803 | -| 47 | 47 | 111 | 175 | 239 | | ||

| 804 | -| 48 | 48 | 112 | 176 | 240 | | ||

| 805 | -| 49 | 49 | 113 | 177 | 241 | | ||

| 806 | -| 50 | 50 | 114 | 178 | 242 | | ||

| 807 | -| 51 | 51 | 115 | 179 | 243 | | ||

| 808 | -| 52 | 52 | 116 | 180 | 244 | | ||

| 809 | -| 53 | 53 | 117 | 181 | 245 | | ||

| 810 | -| 54 | 54 | 118 | 182 | 246 | | ||

| 811 | -| 55 | 55 | 119 | 183 | 247 | | ||

| 812 | -| 56 | 56 | 120 | 184 | 248 | | ||

| 813 | -| 57 | 57 | 121 | 185 | 249 | | ||

| 814 | -| 58 | 58 | 122 | 186 | 250 | | ||

| 815 | -| 59 | 59 | 123 | 187 | 251 | | ||

| 816 | -| 60 | 60 | 124 | 188 | 252 | | ||

| 817 | -| 61 | 61 | 125 | 189 | 253 | | ||

| 818 | -| 62 | 62 | 126 | 190 | 254 | | ||

| 819 | -| 63 | 63 | 127 | 191 | 255 | | ||

| 820 | - | ||

| 821 | - | ||

| 822 | -The same process can be applied in the next round to perform NTT stage 3 and 4\. | ||

| 823 | - | ||

| 824 | -| 0 | → |||||||| | ||

| 825 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 826 | -| 64 ||||||||| | ||

| 827 | -| 128 ||||||||| | ||

| 828 | -| 192 ||||||||| | ||

| 829 | - | ||

| 830 | - | ||

| 831 | -Cycle 0 reading address 0 | ||

| 832 | - | ||

| 833 | -| 16 | → |||| 0 |||| | ||

| 834 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 835 | -| 80 |||| 64 ||||| | ||

| 836 | -| 144 ||| 128 |||||| | ||

| 837 | -| 208 || 192 ||||||| | ||

| 838 | - | ||

| 839 | - | ||

| 840 | -Cycle 1 reading address 16 | ||

| 841 | - | ||

| 842 | -| 32 | → |||| 16 | 0 ||| | ||

| 843 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 844 | -| 96 |||| 80 | 64 |||| | ||

| 845 | -| 160 ||| 144 | 128 ||||| | ||

| 846 | -| 224 || 208 | 192 |||||| | ||

| 847 | - | ||

| 848 | - | ||

| 849 | -Cycle 2 reading address 32 | ||

| 850 | - | ||

| 851 | -| 48 | → |||| 32 | 16 | 0 || | ||

| 852 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 853 | -| 112 |||| 96 | 80 | 64 ||| | ||

| 854 | -| 176 ||| 160 | 144 | 128 |||| | ||

| 855 | -| 240 || 224 | 208 | 192 ||||| | ||

| 856 | - | ||

| 857 | - | ||

| 858 | -Cycle 3 reading address 48 | ||

| 859 | - | ||

| 860 | -| 1 | → |||| 48 | 32 | 16 | 0 | | ||

| 861 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 862 | -| 65 |||| 112 | 96 | 80 | 64 || | ||

| 863 | -| 129 ||| 176 | 160 | 144 | 128 ||| | ||

| 864 | -| 193 || 240 | 224 | 208 | 192 |||| | ||

| 865 | - | ||

| 866 | - | ||

| 867 | -Cycle 4 reading address 1 | ||

| 868 | - | ||

| 869 | -| 17 | → |||| 1 | 48 | 32 | 16 | | ||

| 870 | -| :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | :-: | | ||

| 871 | -| 81 |||| 65 | 112 | 96 | 80 | 64 | | ||

| 872 | -| 145 ||| 129 | 176 | 160 | 144 | 128 || | ||

| 873 | -| 209 || 193 | 240 | 224 | 208 | 192 ||| | ||

| 874 | - | ||

| 875 | - | ||

| 876 | -Cycle 5 reading address 17 | ||

| 877 | - | ||

| 878 | -After completing all stages, the memory contents would be as follows: | ||

| 879 | - | ||

| 880 | -| Address | Memory Content after Stage 7&8 |||| | ||

| 881 | -| ------- | ------------------------------ | --- | --- | --- | | ||

| 882 | -|||||| | ||

| 883 | -| 0 | 0 | 1 | 2 | 3 | | ||

| 884 | -| 1 | 4 | 5 | 6 | 7 | | ||

| 885 | -| 2 | 8 | 9 | 10 | 11 | | ||

| 886 | -| 3 | 12 | 13 | 14 | 15 | | ||

| 887 | -| 4 | 16 | 17 | 18 | 19 | | ||

| 888 | -| 5 | 20 | 21 | 22 | 23 | | ||

| 889 | -| 6 | 24 | 25 | 26 | 27 | | ||

| 890 | -| 7 | 28 | 29 | 30 | 31 | | ||

| 891 | -| 8 | 32 | 33 | 34 | 35 | | ||

| 892 | -| 9 | 36 | 37 | 38 | 39 | | ||

| 893 | -| 10 | 40 | 41 | 42 | 43 | | ||

| 894 | -| 11 | 44 | 45 | 46 | 47 | | ||

| 895 | -| 12 | 48 | 49 | 50 | 51 | | ||

| 896 | -| 13 | 52 | 53 | 54 | 55 | | ||

| 897 | -| 14 | 56 | 57 | 58 | 59 | | ||

| 898 | -| 15 | 60 | 61 | 62 | 63 | | ||

| 899 | -| 16 | 64 | 65 | 66 | 67 | | ||

| 900 | -| 17 | 68 | 69 | 70 | 71 | | ||

| 901 | -| 18 | 72 | 73 | 74 | 75 | | ||

| 902 | -| 19 | 76 | 77 | 78 | 79 | | ||

| 903 | -| 20 | 80 | 81 | 82 | 83 | | ||

| 904 | -| 21 | 84 | 85 | 86 | 87 | | ||

| 905 | -| 22 | 88 | 89 | 90 | 91 | | ||

| 906 | -| 23 | 92 | 93 | 94 | 95 | | ||

| 907 | -| 24 | 96 | 97 | 98 | 99 | | ||

| 908 | -| 25 | 100 | 101 | 102 | 103 | | ||

| 909 | -| 26 | 104 | 105 | 106 | 107 | | ||

| 910 | -| 27 | 108 | 109 | 110 | 111 | | ||

| 911 | -| 28 | 112 | 113 | 114 | 115 | | ||

| 912 | -| 29 | 116 | 117 | 118 | 119 | | ||

| 913 | -| 30 | 120 | 121 | 122 | 123 | | ||

| 914 | -| 31 | 124 | 125 | 126 | 127 | | ||

| 915 | -| 32 | 128 | 129 | 130 | 131 | | ||

| 916 | -| 33 | 132 | 133 | 134 | 135 | | ||

| 917 | -| 34 | 136 | 137 | 138 | 139 | | ||

| 918 | -| 35 | 140 | 141 | 142 | 143 | | ||

| 919 | -| 36 | 144 | 145 | 146 | 147 | | ||

| 920 | -| 37 | 148 | 149 | 150 | 151 | | ||

| 921 | -| 38 | 152 | 153 | 154 | 155 | | ||

| 922 | -| 39 | 156 | 157 | 158 | 159 | | ||

| 923 | -| 40 | 160 | 161 | 162 | 163 | | ||

| 924 | -| 41 | 164 | 165 | 166 | 167 | | ||

| 925 | -| 42 | 168 | 169 | 170 | 171 | | ||

| 926 | -| 43 | 172 | 173 | 174 | 175 | | ||

| 927 | -| 44 | 176 | 177 | 178 | 179 | | ||

| 928 | -| 45 | 180 | 181 | 182 | 183 | | ||

| 929 | -| 46 | 184 | 185 | 186 | 187 | | ||

| 930 | -| 47 | 188 | 189 | 190 | 191 | | ||

| 931 | -| 48 | 192 | 193 | 194 | 195 | | ||

| 932 | -| 49 | 196 | 197 | 198 | 199 | | ||

| 933 | -| 50 | 200 | 201 | 202 | 203 | | ||

| 934 | -| 51 | 204 | 205 | 206 | 207 | | ||

| 935 | -| 52 | 208 | 209 | 210 | 211 | | ||

| 936 | -| 53 | 212 | 213 | 214 | 215 | | ||

| 937 | -| 54 | 216 | 217 | 218 | 219 | | ||

| 938 | -| 55 | 220 | 221 | 222 | 223 | | ||

| 939 | -| 56 | 224 | 225 | 226 | 227 | | ||

| 940 | -| 57 | 228 | 229 | 230 | 231 | | ||

| 941 | -| 58 | 232 | 233 | 234 | 235 | | ||

| 942 | -| 59 | 236 | 237 | 238 | 239 | | ||

| 943 | -| 60 | 240 | 241 | 242 | 243 | | ||

| 944 | -| 61 | 244 | 245 | 246 | 247 | | ||

| 945 | -| 62 | 248 | 249 | 250 | 251 | | ||

| 946 | -| 63 | 252 | 253 | 254 | 255 | | ||

| 947 | - | ||

| 948 | - | ||

| 949 | -The proposed method saves the time needed for shuffling and reordering, while using only a little more memory. | ||

| 950 | - | ||

| 951 | -With this memory access pattern, writes to the memory are in order (0, 1, 2, 3, etc) while reads wraparound with a step of 16 (0, 16, 32 48, 1, 17, 33, 49, etc). Hence, there will be a memory conflict where writes to addresses take place before the data is read and provided to the butterfly 2x2 module. To resolve this, a set of 3 base addresses are given to the NTT module – src address, interim address and dest address that belong to 3 separate sections in memory. The NTT module will access the memory with the appropriate base address for each round as follows: | ||

| 952 | - | ||

| 953 | -| Round | Read base address | Write base address | | ||

| 954 | -| :---- | :---------------- | :----------------- | | ||

| 955 | -| 0 | src | interim | | ||

| 956 | -| 1 | interim | dest | | ||

| 957 | -| 2 | dest | interim | | ||

| 958 | -| 3 | interim | dest | | ||

| 959 | - | ||

| 960 | - | ||

| 961 | -At the end of NTT operation, results must be located in the section with the dest base address. This will also provide the benefit of preserving the original input for later use in keygen or signing operations. The same memory access pattern is followed for INTT operation as well. Note that Adam’s bridge controller may choose to make src and dest base addresses the same to save on memory usage, when original coefficients need not be preserved. In this case, the requirement is still to have a separate interim base address to avoid memory conflicts during NTT operation. | ||

| 962 | - | ||

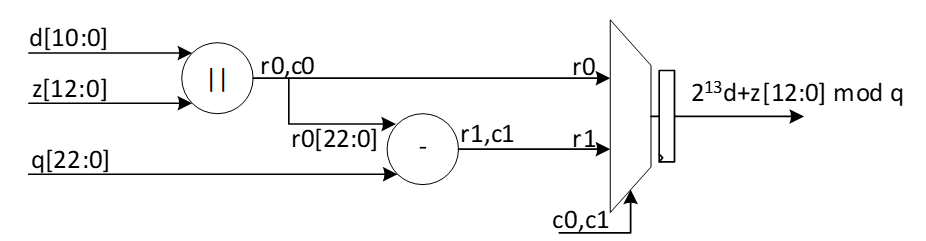

| 963 | -#### Modular Reduction in NTT | ||

| 964 | - | ||

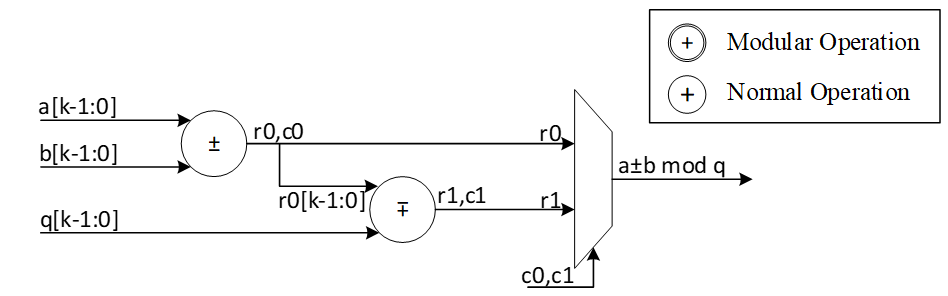

| 965 | -The modular addition/subtraction in hardware platform can be implemented by one additional subtraction/addition operations, as follows: | ||

| 966 | - | ||

| 967 | - | ||

| 968 | - | ||

| 969 | -However, modular multiplication can be implemented using different techniques. The commonly used Barrett reduction and Montgomery reduction require additional multiplications and are more suitable for the non-specific modulus. Furthermore, Montgomery reduction needs two more steps to convert all inputs from normal domain to Montgomery domain and then convert back the results into normal domain. This conversation increases the latency of NTT operations and does not lead to the best performance. Hence, Barrett reduction and Montgomery reduction are expensive in time and hardware resources. | ||

| 970 | - | ||

| 971 | - | ||

| 972 | - | ||

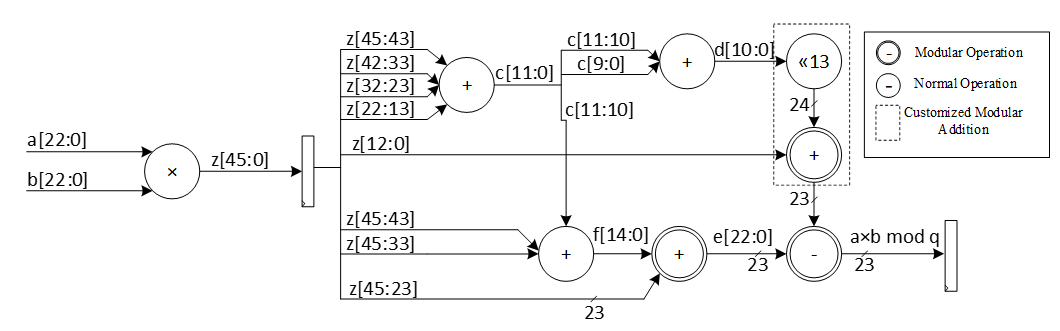

| 973 | -For Dilithium hardware accelerator, we can customize the reduction architecture based on the prime value of the scheme with q= 8,380,417 to design a hardware-friendly architecture that increase the efficiency of computation. The value of q can be presented by: | ||

| 974 | - | ||

| 975 | -q=8,380,417=223-213+1 | ||

| 976 | - | ||

| 977 | -For the modular operation we have: | ||

| 978 | - | ||

| 979 | -223=213-1 mod q | ||

| 980 | - | ||

| 981 | -Suppose that all input operands are less than q, we have: | ||

| 982 | - | ||

| 983 | -0≤a,b\<q | ||

| 984 | - | ||

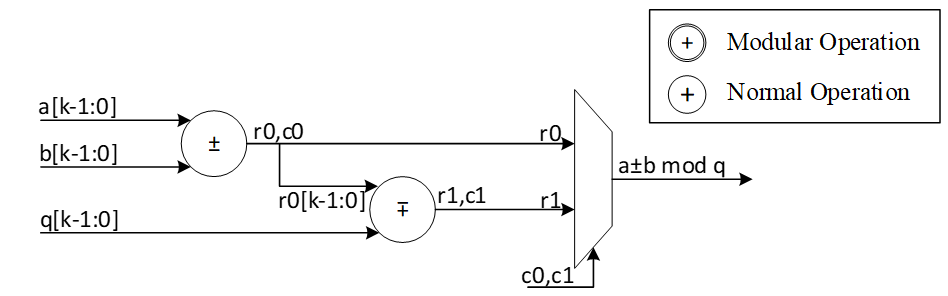

| 985 | -z=a.b\<q2=46'h3FE0\_04FF\_C001 | ||

| 986 | - | ||

| 987 | -Based on 223=213-1 mod q, we can rewrite the equation as follows: | ||

| 988 | - | ||

| 989 | -z=223z45:23+z22:0=213z45:23-z45:23+z22:0=223z45:33+213z32:23-z45:23+z22:0=213z45:33-z45:33+213z32:23-z45:23+z22:0=223z45:43+213z42:33-z45:33+213z32:23-z45:23+z22:0=213z45:43-z45:43+213z42:33-z45:33+213z32:23-z45:23+z22:0=213z45:43+z42:33+z32:23+-z45:43-z45:33-z45:23+z22:0=213z45:43+z42:33+z32:23+z22:13+-z45:43-z45:33-z45:23+z12:0=213c-(z45:43+z45:33+z45:23)+z\[12:0\] | ||

| 990 | - | ||

| 991 | -Where: | ||

| 992 | - | ||

| 993 | -c=z45:43+z42:33+z32:23+z\[22:13\]\<212 | ||

| 994 | - | ||

| 995 | -The value of c has 12 bits, and we can rewrite it as follows: | ||

| 996 | - | ||

| 997 | -213c11:0=223c11:10+213c9:0=213c11:10-c11:10+213c9:0=213d-c11:10 | ||

| 998 | - | ||

| 999 | -d=c11:10+c9:0 | ||

| 1000 | - | ||

| 1001 | -So, the value of z mod q is as follows: | ||

| 1002 | - | ||

| 1003 | -z=213c-z45:43+z45:33+z45:23+z12:0=213d+z12:0-z45:43+z45:33+z45:23+c11:10=213d+z12:0-e | ||

| 1004 | - | ||

| 1005 | -Where: | ||

| 1006 | - | ||

| 1007 | -e=z45:43+z45:33+z45:23+c11:10=f+z45:23 mod q | ||

| 1008 | - | ||

| 1009 | -f\[14:0\]=z45:43+z45:33+c11:10 | ||

| 1010 | - | ||

| 1011 | -We use a modular addition for f+z45:23 to keep it less than q. This modular addition has one stage delay. | ||

| 1012 | - | ||

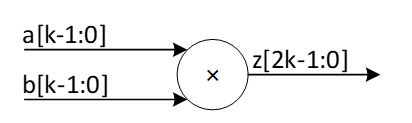

| 1013 | -The addition between 213d and z12:0 can be implemented by concatenating since the first 13 bits of d are zero as follows: | ||

| 1014 | - | ||

| 1015 | -g23:0=213d+z12:0=d10:0||z\[12:0\] | ||

| 1016 | - | ||

| 1017 | -Since the result has more than 23 bits, we perform a modular addition to keep it less than q. For that, the regular modular addition will be replaced by the following architecture while c0=g23, r0=g\[22:0\]. In other words, c0=d10, r0\[22:0\]=d9:0||z\[12:0\] | ||

| 1018 | - | ||

| 1019 | - | ||

| 1020 | - | ||

| 1021 | -The following figure shows the architecture of this reduction technique. As one can see, these functions do not need any multiplications in hardware and can be achieved by shifter and adder. | ||

| 1022 | - | ||

| 1023 | - | ||

| 1024 | - | ||

| 1025 | -The modular multiplication is implemented with a 3-stage pipeline architecture. At the first pipeline stage, z=a·b is calculated. At the second pipeline stage, f+z\[45:23\] and 213d+z12:0 are calculated in parallel. At the third pipeline stage, a modular subtraction is executed to obtain the result and the result is output. | ||

| 1026 | - | ||

| 1027 | -We do not need extra multiplications for our modular reduction, unlike Barrett and Montgomery algorithms. The operations of our reduction do not depend on the input data and do not leak any information. Our reduction using the modulus q= 8,380,417 is fast, efficient and constant-time. | ||

| 1028 | - | ||

| 1029 | -### Performance of NTT | ||

| 1030 | - | ||

| 1031 | -For a complete NTT operation with 8 layers, i.e., n \= 256, the proposed architecture takes 82=4 rounds. Each round involves 2564=64 operations in pipelined architecture. Hence, the latency of each round is equal to 64 (read from memory) \+ 8 (2 sequential butterfly latency) \+ 4 (input buffer latency) \+ 2 (wait between each two stages) \= 78 cycles. | ||

| 1032 | - | ||

| 1033 | -Round 0: stage 0 & 1 | ||

| 1034 | - | ||

| 1035 | -Round 1: stage 2 & 3 | ||

| 1036 | - | ||

| 1037 | -Round 2: stage 4 & 5 | ||

| 1038 | - | ||

| 1039 | -Round 3: stage 6 & 7 | ||

| 1040 | - | ||

| 1041 | -The total latency would be 4×78=312 cycles. | ||

| 1042 | - | ||

| 1043 | -For a complete NTT/INTT operation for Dilithium ML-DSA-87 with 7 or 8 polynomials, 7\*312=2184 or 8\*312=2496 cycles are required. However, our design can be duplicated to enable parallel NTT for two different polynomials. Having two parallel design results in 1248 cycles. | ||

| 1044 | - | ||

| 1045 | -### NTT shuffling countermeasure | ||

| 1046 | - | ||

| 1047 | -To protect NTT, we have two options – shuffling the order of execution of coefficients and masking in-order computation such that NTT performs operation on two input shares per coefficient and produces two output shares. While masking is a strong countermeasure for side-channel attacks, it requires at least 4x the area and adds 4x the latency to one NTT operation. Shuffling is an implementation trick that can be used to provide randomization to some degree without area or latency overhead. In Adam’s Bridge, we employ a combination of both for protected design. One NTT core will have shuffling for both NTT and INTT modes. The second NTT core will have shuffling and masking on the first layer of computation for INTT mode with cascaded connection from a masked PWM module. In NTT mode, the second NTT core will employ only shuffling. PWM operations are masked by default. PWA and PWS operations are shuffled by default. | ||

| 1048 | - | ||

| 1049 | -| Address || Memory Content |||| | ||

| 1050 | -| ------- | --- | -------------- | --- | --- | --- | | ||

| 1051 | -||||||| | ||

| 1052 | -| 0 || 0 | 1 | 2 | 3 | | ||

| 1053 | -| 1 || 4 | 5 | 6 | 7 | | ||

| 1054 | -| 2 || 8 | 9 | 10 | 11 | | ||

| 1055 | -| 3 || 12 | 13 | 14 | 15 | | ||

| 1056 | -| 4 || 16 | 17 | 18 | 19 | | ||

| 1057 | -| 5 || 20 | 21 | 22 | 23 | | ||

| 1058 | -| 6 || 24 | 25 | 26 | 27 | | ||

| 1059 | -| 7 || 28 | 29 | 30 | 31 | | ||

| 1060 | -| 8 || 32 | 33 | 34 | 35 | | ||

| 1061 | -| 9 || 36 | 37 | 38 | 39 | | ||

| 1062 | -| 10 || 40 | 41 | 42 | 43 | | ||

| 1063 | -| 11 || 44 | 45 | 46 | 47 | | ||

| 1064 | -| 12 || 48 | 49 | 50 | 51 | | ||

| 1065 | -| 13 || 52 | 53 | 54 | 55 | | ||

| 1066 | -| 14 || 56 | 57 | 58 | 59 | | ||

| 1067 | -| 15 || 60 | 61 | 62 | 63 | | ||

| 1068 | -| 16 || 64 | 65 | 66 | 67 | | ||

| 1069 | -| 17 || 68 | 69 | 70 | 71 | | ||

| 1070 | -| 18 || 72 | 73 | 74 | 75 | | ||

| 1071 | -| 19 || 76 | 77 | 78 | 79 | | ||

| 1072 | -| 20 || 80 | 81 | 82 | 83 | | ||

| 1073 | -| 21 || 84 | 85 | 86 | 87 | | ||

| 1074 | -| 22 || 88 | 89 | 90 | 91 | | ||

| 1075 | -| 23 || 92 | 93 | 94 | 95 | | ||

| 1076 | -| 24 || 96 | 97 | 98 | 99 | | ||

| 1077 | -| 25 || 100 | 101 | 102 | 103 | | ||

| 1078 | -| 26 || 104 | 105 | 106 | 107 | | ||

| 1079 | -| 27 || 108 | 109 | 110 | 111 | | ||

| 1080 | -| 28 || 112 | 113 | 114 | 115 | | ||

| 1081 | -| 29 || 116 | 117 | 118 | 119 | | ||

| 1082 | -| 30 || 120 | 121 | 122 | 123 | | ||

| 1083 | -| 31 || 124 | 125 | 126 | 127 | | ||

| 1084 | -| 32 || 128 | 129 | 130 | 131 | | ||

| 1085 | -| 33 || 132 | 133 | 134 | 135 | | ||

| 1086 | -| 34 || 136 | 137 | 138 | 139 | | ||

| 1087 | -| 35 || 140 | 141 | 142 | 143 | | ||

| 1088 | -| 36 || 144 | 145 | 146 | 147 | | ||

| 1089 | -| 37 || 148 | 149 | 150 | 151 | | ||

| 1090 | -| 38 || 152 | 153 | 154 | 155 | | ||

| 1091 | -| 39 || 156 | 157 | 158 | 159 | | ||

| 1092 | -| 40 || 160 | 161 | 162 | 163 | | ||

| 1093 | -| 41 || 164 | 165 | 166 | 167 | | ||

| 1094 | -| 42 || 168 | 169 | 170 | 171 | | ||

| 1095 | -| 43 || 172 | 173 | 174 | 175 | | ||

| 1096 | -| 44 || 176 | 177 | 178 | 179 | | ||

| 1097 | -| 45 || 180 | 181 | 182 | 183 | | ||

| 1098 | -| 46 || 184 | 185 | 186 | 187 | | ||

| 1099 | -| 47 || 188 | 189 | 190 | 191 | | ||

| 1100 | -| 48 || 192 | 193 | 194 | 195 | | ||

| 1101 | -| 49 || 196 | 197 | 198 | 199 | | ||

| 1102 | -| 50 || 200 | 201 | 202 | 203 | | ||

| 1103 | -| 51 || 204 | 205 | 206 | 207 | | ||

| 1104 | -| 52 || 208 | 209 | 210 | 211 | | ||

| 1105 | -| 53 || 212 | 213 | 214 | 215 | | ||

| 1106 | -| 54 || 216 | 217 | 218 | 219 | | ||

| 1107 | -| 55 || 220 | 221 | 222 | 223 | | ||

| 1108 | -| 56 || 224 | 225 | 226 | 227 | | ||

| 1109 | -| 57 || 228 | 229 | 230 | 231 | | ||

| 1110 | -| 58 || 232 | 233 | 234 | 235 | | ||

| 1111 | -| 59 || 236 | 237 | 238 | 239 | | ||

| 1112 | -| 60 || 240 | 241 | 242 | 243 | | ||

| 1113 | -| 61 || 244 | 245 | 246 | 247 | | ||

| 1114 | -| 62 || 248 | 249 | 250 | 251 | | ||

| 1115 | -| 63 || 252 | 253 | 254 | 255 | | ||

| 1116 | - | ||

| 1117 | - | ||

| 1118 | -To implement shuffling in NTT, the memory content is divided into 16 chunks. The highlighted section in the memory table above shows the 16 chunk start addresses. For example, the first chunk consists of addresses 0, 16, 32, 48\. Second chunk has 1, 17, 33, 49, and so on. In NTT mode, memory read pattern is 0, 16, 32, 48, 1, 17, 33, 49, etc. The buffer in NTT module is updated to have two sections and is addressable to support INTT shuffling with matched search space as that of NTT mode. | ||

| 1119 | - | ||

| 1120 | -During shuffling, two levels of randomization are done: | ||

| 1121 | - | ||

| 1122 | -1. Chunk order is randomized | ||

| 1123 | -2. Start address within the selected chunk is also randomized. | ||

| 1124 | - | ||

| 1125 | -With this technique, the search space is 16 ×416=236. For example, if chunk 5 is selected as the starting chunk, the input buffer in NTT mode is configured as below. | ||

| 1126 | - | ||

| 1127 | -||||| | ||

| 1128 | -| :--- | :--- | :--- | :--- | | ||

| 1129 | -||||| | ||

| 1130 | -||||| | ||

| 1131 | -||||| | ||

| 1132 | -| 2151 | 2140 | 2133 | 2122 | | ||

| 1133 | -| 1511 | 1500 | 1493 | 1482 | | ||

| 1134 | -| 871 | 860 | 853 | 842 | | ||

| 1135 | -| 231 | 220 | 213 | 202 | | ||

| 1136 | - | ||

| 1137 | - | ||