v1.2: CONFIGOPTS.png

v2.0: CONFIGOPTS.png

Image not present in this version

| @@ -1,12 +1,12 @@ | |||

| 1 | 1 | <div style="font-size: 0.85em; color: #656d76; margin-bottom: 1em; padding: 0.5em; background: #f6f8fa; border-radius: 4px;"> | |

| 2 | -📄 Source: <a href="https://github.com/chipsalliance/caliptra-rtl/blob/5f85fb4bc95b753a2f7d042db7dc2644ca1e8c49/docs/CaliptraHardwareSpecification.md" target="_blank">chipsalliance/caliptra-rtl/docs/CaliptraHardwareSpecification.md</a> @ <code>5f85fb4</code> | ||

| 2 | +📄 Source: <a href="https://github.com/chipsalliance/caliptra-rtl/blob/35b0bc5691b2bd0fc180403914cfabe207379089/docs/CaliptraHardwareSpecification.md" target="_blank">chipsalliance/caliptra-rtl/docs/CaliptraHardwareSpecification.md</a> @ <code>35b0bc5</code> | ||

| 3 | 3 | </div> | |

| 4 | 4 | ||

| 5 | 5 |  | |

| 6 | 6 | ||

| 7 | 7 | <p style="text-align: center;">Caliptra Hardware Specification</p> | |

| 8 | 8 | ||

| 9 | -<p style="text-align: center;">Version 1.1</p> | ||

| 9 | +<p style="text-align: center;">Revision 2.0.3</p> | ||

| 10 | 10 | ||

| 11 | 11 | <div style="page-break-after: always"></div> | |

| 12 | 12 | ||

| @@ -21,6 +21,23 @@ | |||

| 21 | 21 | # Caliptra Core | |

| 22 | 22 | ||

| 23 | 23 | For information on the Caliptra Core, see the [High level architecture](https://chipsalliance.github.io/Caliptra/doc/Caliptra.html#high-level-architecture) section of [Caliptra: A Datacenter System on a Chip (SoC) Root of Trust (RoT)](https://chipsalliance.github.io/Caliptra/doc/Caliptra.html). | |

| 24 | + | ||

| 25 | +## Key Caliptra Core 2.0 Changes | ||

| 26 | +* AXI subordinate replaces APB interface of Caliptra 1.x hardware | ||

| 27 | +* SHA Accelerator functionality now available exclusively to Caliptra | ||

| 28 | + * Caliptra uC may use internally in mailbox mode or via the Caliptra AXI DMA assist engine in streaming mode | ||

| 29 | + * SHA Accelerator adds new SHA save/restore functionality | ||

| 30 | +* Adams Bridge Dilithium/ML-DSA (refer to [Adams bridge spec](https://github.com/chipsalliance/adams-bridge/blob/main/docs/AdamsBridgeHardwareSpecification.md)) | ||

| 31 | +* Subsystem mode support (refer to [Subsystem Specification](https://github.com/chipsalliance/caliptra-ss/blob/main/docs/Caliptra%202.0%20Subsystem%20Specification%201.pdf) for details) | ||

| 32 | + * ECDH hardware support | ||

| 33 | + * HMAC512 hardware support | ||

| 34 | + * AXI Manager with DMA support (refer to [DMA Specification](https://github.com/chipsalliance/caliptra-ss/blob/main/docs/CaliptraSSHardwareSpecification.md#caliptra-axi-manager--dma-assist)) | ||

| 35 | + * Manufacturing and Debug Unlock | ||

| 36 | + * UDS programming | ||

| 37 | + * Read logic for Secret Fuses | ||

| 38 | + * Streaming Boot Support | ||

| 39 | +* RISC-V core PMP support | ||

| 40 | +* CSR HMAC key for manufacturing flow | ||

| 24 | 41 | ||

| 25 | 42 | ## Boot FSM | |

| 26 | 43 | ||

| @@ -57,12 +74,13 @@ | |||

| 57 | 74 | | Parameter | Configuration | | |

| 58 | 75 | | :---------------------- | :------------ | | |

| 59 | 76 | | Interface | AHB-Lite | | |

| 60 | -| DCCM | 128 KiB | | ||

| 61 | -| ICCM | 128 KiB | | ||

| 77 | +| DCCM | 256 KiB | | ||

| 78 | +| ICCM | 256 KiB | | ||

| 62 | 79 | | I-Cache | Disabled | | |

| 63 | 80 | | Reset Vector | 0x00000000 | | |

| 64 | 81 | | Fast Interrupt Redirect | Enabled | | |

| 65 | 82 | | External Interrupts | 31 | | |

| 83 | +| PMP | Enabled | | ||

| 66 | 84 | ||

| 67 | 85 | ||

| 68 | 86 | ### Embedded memory export | |

| @@ -75,12 +93,12 @@ | |||

| 75 | 93 | ||

| 76 | 94 | | Subsystem | Address size | Start address | End address | | |

| 77 | 95 | | :------------------ | :----------- | :------------ | :---------- | | |

| 78 | -| ROM | 48 KiB | 0x0000_0000 | 0x0000_BFFF | | ||

| 96 | +| ROM | 96 KiB | 0x0000_0000 | 0x0000_BFFF | | ||

| 79 | 97 | | Cryptographic | 512 KiB | 0x1000_0000 | 0x1007_FFFF | | |

| 80 | 98 | | Peripherals | 32 KiB | 0x2000_0000 | 0x2000_7FFF | | |

| 81 | -| SoC IFC | 256 KiB | 0x3000_0000 | 0x3003_FFFF | | ||

| 82 | -| RISC-V Core ICCM | 128 KiB | 0x4000_0000 | 0x4001_FFFF | | ||

| 83 | -| RISC-V Core DCCM | 128 KiB | 0x5000_0000 | 0x5001_FFFF | | ||

| 99 | +| SoC IFC | 512 KiB | 0x3000_0000 | 0x3007_FFFF | | ||

| 100 | +| RISC-V Core ICCM | 256 KiB | 0x4000_0000 | 0x4003_FFFF | | ||

| 101 | +| RISC-V Core DCCM | 256 KiB | 0x5000_0000 | 0x5003_FFFF | | ||

| 84 | 102 | | RISC-V MM CSR (PIC) | 256 MiB | 0x6000_0000 | 0x6FFF_FFFF | | |

| 85 | 103 | ||

| 86 | 104 | ||

| @@ -92,12 +110,14 @@ | |||

| 92 | 110 | | :---------------------------------- | :-------- | :----------- | :------------ | :---------- | | |

| 93 | 111 | | Cryptographic Initialization Engine | 0 | 32 KiB | 0x1000_0000 | 0x1000_7FFF | | |

| 94 | 112 | | ECC Secp384 | 1 | 32 KiB | 0x1000_8000 | 0x1000_FFFF | | |

| 95 | -| HMAC384 | 2 | 4 KiB | 0x1001_0000 | 0x1001_0FFF | | ||

| 113 | +| HMAC512 | 2 | 4 KiB | 0x1001_0000 | 0x1001_0FFF | | ||

| 96 | 114 | | Key Vault | 3 | 8 KiB | 0x1001_8000 | 0x1001_9FFF | | |

| 97 | 115 | | PCR Vault | 4 | 8 KiB | 0x1001_A000 | 0x1001_BFFF | | |

| 98 | 116 | | Data Vault | 5 | 8 KiB | 0x1001_C000 | 0x1001_DFFF | | |

| 99 | 117 | | SHA512 | 6 | 32 KiB | 0x1002_0000 | 0x1002_7FFF | | |

| 100 | -| SHA256 | 13 | 32 KiB | 0x1002_8000 | 0x1002_FFFF | | ||

| 118 | +| SHA256 | 10 | 32 KiB | 0x1002_8000 | 0x1002_FFFF | | ||

| 119 | +| ML-DSA | 14 | 64 KiB | 0x1003_0000 | 0x1003_FFFF | | ||

| 120 | +| AES | 15 | 4 KiB | 0x1001_1000 | 0x1001_1FFF | | ||

| 101 | 121 | ||

| 102 | 122 | ||

| 103 | 123 | #### Peripherals subsystem | |

| @@ -106,10 +126,8 @@ | |||

| 106 | 126 | ||

| 107 | 127 | | IP/Peripheral | Target \# | Address size | Start address | End address | | |

| 108 | 128 | | :------------ | :-------- | :----------- | :------------ | :---------- | | |

| 109 | -| QSPI | 7 | 4 KiB | 0x2000_0000 | 0x2000_0FFF | | ||

| 110 | -| UART | 8 | 4 KiB | 0x2000_1000 | 0x2000_1FFF | | ||

| 111 | -| CSRNG | 15 | 4 KiB | 0x2000_2000 | 0x2000_2FFF | | ||

| 112 | -| ENTROPY SRC | 16 | 4 KiB | 0x2000_3000 | 0x2000_3FFF | | ||

| 129 | +| CSRNG | 12 | 4 KiB | 0x2000_2000 | 0x2000_2FFF | | ||

| 130 | +| ENTROPY SRC | 13 | 4 KiB | 0x2000_3000 | 0x2000_3FFF | | ||

| 113 | 131 | ||

| 114 | 132 | ||

| 115 | 133 | #### SoC interface subsystem | |

| @@ -118,10 +136,11 @@ | |||

| 118 | 136 | ||

| 119 | 137 | | IP/Peripheral | Target \# | Address size | Start address | End address | | |

| 120 | 138 | | :------------------------- | :-------- | :----------- | :------------ | :---------- | | |

| 121 | -| Mailbox SRAM Direct Access | 10 | 128 KiB | 0x3000_0000 | 0x3001_FFFF | | ||

| 122 | -| Mailbox CSR | 10 | 4 KiB | 0x3002_0000 | 0x3002_0FFF | | ||

| 123 | -| SHA512 Accelerator CSR | 10 | 4 KiB | 0x3002_1000 | 0x3002_1FFF | | ||

| 124 | -| Mailbox | 10 | 64 KiB | 0x3003_0000 | 0x3003_FFFF | | ||

| 139 | +| Mailbox CSR | 7 | 4 KiB | 0x3002_0000 | 0x3002_0FFF | | ||

| 140 | +| SHA512 Accelerator | 7 | 4 KiB | 0x3002_1000 | 0x3002_1FFF | | ||

| 141 | +| AXI DMA | 7 | 4 KiB | 0x3002_2000 | 0x3002_2FFF | | ||

| 142 | +| SOC IFC CSR | 7 | 64 KiB | 0x3003_0000 | 0x3003_FFFF | | ||

| 143 | +| Mailbox SRAM Direct Access | 7 | 256 KiB | 0x3004_0000 | 0x3007_FFFF | | ||

| 125 | 144 | ||

| 126 | 145 | ||

| 127 | 146 | #### RISC-V core local memory blocks | |

| @@ -130,8 +149,8 @@ | |||

| 130 | 149 | ||

| 131 | 150 | | IP/Peripheral | Target \# | Address size | Start address | End address | | |

| 132 | 151 | | :-------------- | :-------- | :----------- | :------------ | :---------- | | |

| 133 | -| ICCM0 (via DMA) | 12 | 128 KiB | 0x4000_0000 | 0x4001_FFFF | | ||

| 134 | -| DCCM | 11 | 128 KiB | 0x5000_0000 | 0x5001_FFFF | | ||

| 152 | +| ICCM0 (via DMA) | 9 | 256 KiB | 0x4000_0000 | 0x4003_FFFF | | ||

| 153 | +| DCCM | 8 | 256 KiB | 0x5000_0000 | 0x5003_FFFF | | ||

| 135 | 154 | ||

| 136 | 155 | ||

| 137 | 156 | ### Interrupts | |

| @@ -171,14 +190,16 @@ | |||

| 171 | 190 | | SHA512 (Notifications) | 10 | 7 | | |

| 172 | 191 | | SHA256 (Errors) | 11 | 8 | | |

| 173 | 192 | | SHA256 (Notifications) | 12 | 7 | | |

| 174 | -| QSPI (Errors) | 13 | 4 | | ||

| 175 | -| QSPI (Notifications) | 14 | 3 | | ||

| 176 | -| UART (Errors) | 15 | 4 | | ||

| 177 | -| UART (Notifications) | 16 | 3 | | ||

| 178 | -| RESERVED | 17 | 4 | | ||

| 179 | -| RESERVED | 18 | 3 | | ||

| 193 | +| RESERVED | 13, 15, 17 | 4 | | ||

| 194 | +| RESERVED | 14, 16, 18 | 3 | | ||

| 180 | 195 | | Mailbox (Errors) | 19 | 8 | | |

| 181 | 196 | | Mailbox (Notifications) | 20 | 7 | | |

| 197 | +| SHA512 Accelerator (Errors) | 23 | 8 | | ||

| 198 | +| SHA512 Accelerator (Notifications) | 24 | 7 | | ||

| 199 | +| MLDSA (Errors) | 23 | 8 | | ||

| 200 | +| MLDSA (Notifications) | 24 | 7 | | ||

| 201 | +| AXI DMA (Errors) | 25 | 8 | | ||

| 202 | +| AXI DMA (Notifications) | 26 | 7 | | ||

| 182 | 203 | ||

| 183 | 204 | ||

| 184 | 205 | ## Watchdog timer | |

| @@ -230,182 +251,18 @@ | |||

| 230 | 251 | ||

| 231 | 252 | As a result of this implementation, 64-bit data transfers are not supported on the Caliptra AHB fabric. Firmware running on the internal microprocessor may only access memory and registers using a 32-bit or smaller request size, as 64-bit transfer requests will be corrupted. | |

| 232 | 253 | ||

| 254 | +All AHB requests internal to Caliptra must be to an address that is aligned to the native data width of 4-bytes. Any AHB read or write by the Caliptra RISC-V processor that is not aligned to this boundary will fail to decode to the targeted register, will fail to write the submitted data, and will return read data of all zeroes. All AHB requests must also use the native size of 4 bytes (encoded in the hsize signal with a value of 2). The only exception to this is when the RISC-V processor performs byte-aligned, single-byte reads to the Mailbox SRAM using the direct-access mechanism described in [SoC Mailbox](#SoC-mailbox). In this case, a byte-aligned address must be accompanied by the correct size indicator for a single-byte access. Read addresses for byte accesses are aligned to the 4-byte boundary in hardware, and will successfully complete with the correct data at the specified byte offset. Direct mode SRAM writes must be 4-bytes in size and must be aligned to the 4-byte boundary. Hardware writes the entire dword of data to the aligned address, so attempts to write a partial word of data may result in data corruption. | ||

| 255 | + | ||

| 233 | 256 | ## Cryptographic subsystem | |

| 234 | 257 | ||

| 235 | 258 | For details, see the [Cryptographic subsystem architecture](#cryptographic-subsystem-architecture) section. | |

| 236 | 259 | ||

| 237 | -## Peripherals subsystem | ||

| 238 | - | ||

| 239 | -Caliptra includes QSPI and UART peripherals that are used to facilitate alternative operating modes and debug. In the first generation, Caliptra does not support enabling the QSPI interface. Similarly, the UART interface exists to facilitate firmware debug in an FPGA prototype, but should be disabled in final silicon. SystemVerilog defines used to disable these peripherals are described in the [Caliptra Integration Specification](https://github.com/chipsalliance/caliptra-rtl/blob/main/docs/CaliptraIntegrationSpecification.md). Operation of these peripherals is described in the following sections. | ||

| 240 | - | ||

| 241 | -### QSPI Flash Controller | ||

| 242 | - | ||

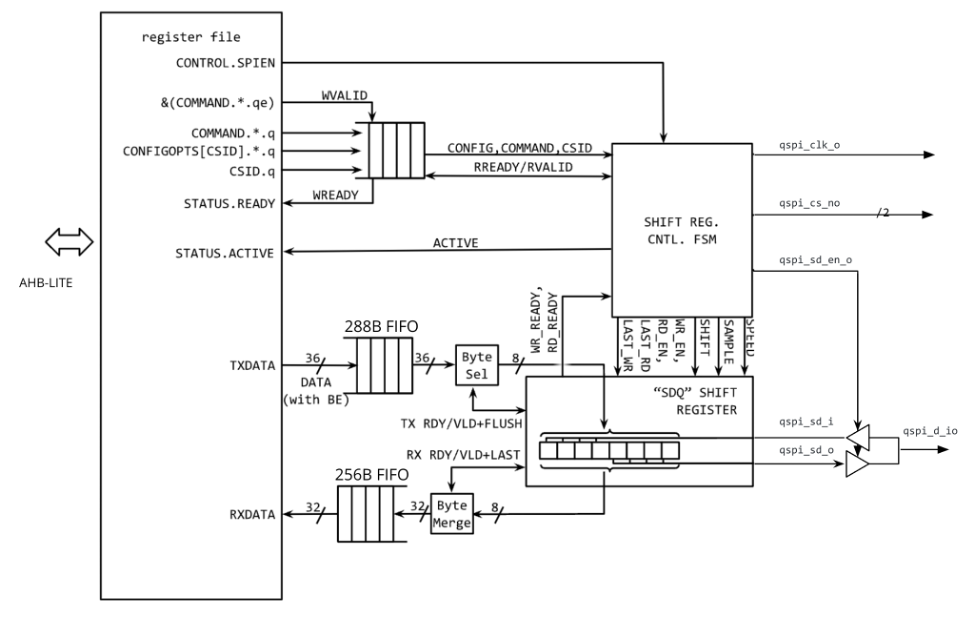

| 243 | -Caliptra implements a QSPI block that can communicate with 2 QSPI devices. This QSPI block is accessible to FW over the AHB-lite Interface. | ||

| 244 | - | ||

| 245 | -The QSPI block is composed of the spi\_host implementation. For information, see the [SPI\_HOST HWIP Technical Specification](https://opentitan.org/book/hw/ip/spi_host/index.html). The core code (see [spi\_host](https://github.com/lowRISC/opentitan/tree/master/hw/ip/spi_host)) is reused but the interface to the module is changed to AHB-lite and the number of chip select lines supported is increased to 2. The design provides support for Standard SPI, Dual SPI, or Quad SPI commands. The following figure shows the QSPI flash controller. | ||

| 246 | - | ||

| 247 | -*Figure 4: QSPI flash controller* | ||

| 248 | - | ||

| 249 | - | ||

| 250 | - | ||

| 251 | -#### Operation | ||

| 252 | - | ||

| 253 | -Transactions flow through the QSPI block starting with AHB-lite writes to the TXDATA FIFO. Commands are then written and processed by the control FSM, orchestrating transmissions from the TXDATA FIFO and receiving data into the RXDATA FIFO. | ||

| 254 | - | ||

| 255 | -The structure of a command depends on the device and the command itself. In the case of a standard SPI device, the host IP always transmits data on qspi\_d\_io[0] and always receives data from the target device on qspi\_d\_io[1]. In Dual or Quad modes, all data lines are bi-directional, thus allowing full bandwidth in transferring data across 4 data lines. | ||

| 256 | - | ||

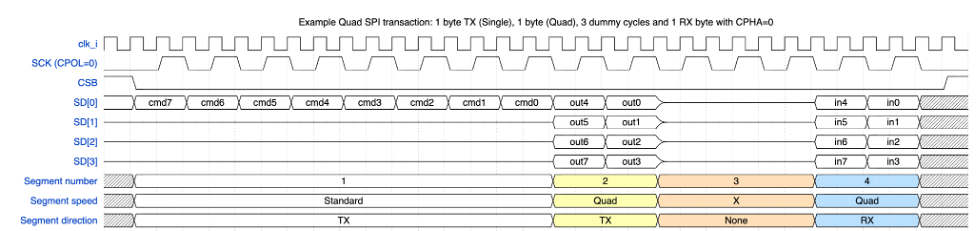

| 257 | -A typical SPI command consists of different segments that are combined as shown in the following example. Each segment can configure the length, speed, and direction. As an example, the following SPI read transaction consists of 2 segments. | ||

| 258 | - | ||

| 259 | -*Figure 5: SPI read transaction segments* | ||

| 260 | - | ||

| 261 | - | ||

| 262 | - | ||

| 263 | -| Segment \# | Length (Bytes) | Speed | Direction | TXDATA FIFO | RXDATA FIFO | | ||

| 264 | -| :--------- | :------------- | :------- | :---------------- | :----------- | :----------------- | | ||

| 265 | -| 1 | 4 | standard | TX <br>qspi_d_io\[0\] | \[0\] 0x3 (ReadData) <br>\[1\] Addr\[23:16\] <br>\[2\] Addr\[15:8\] <br>\[3\] Addr\[7:0\] || | ||

| 266 | -| 2 | 1 | standard | RX <br>qspi_d_io\[1\] || \[0\] Data \[7:0\] | | ||

| 267 | - | ||

| 268 | - | ||

| 269 | -In this example, the ReadData (0x3) command was written to the TXDATA FIFO, followed by the 3B address. This maps to a total of 4 bytes that are transmitted out across qspi\_d\_io[0] in the first segment. The second segment consists of a read command that receives 1 byte of data from the target device across qspi\_d\_io[1]. | ||

| 270 | - | ||

| 271 | -QSPI consists of up to four command segments in which the host: | ||

| 272 | - | ||

| 273 | -1. Transmits instructions or data at the standard rate | ||

| 274 | -2. Transmits instructions address or data on 2 or 4 data lines | ||

| 275 | -3. Holds the bus in a high-impedance state for some number of dummy cycles where neither side transmits | ||

| 276 | -4. Receives information from the target device at the specified rate (derived from the original command) | ||

| 277 | - | ||

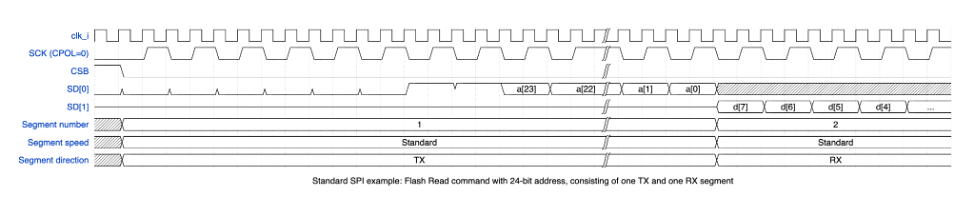

| 278 | -The following example shows the QSPI segments. | ||

| 279 | - | ||

| 280 | -*Figure 6: QSPI segments* | ||

| 281 | - | ||

| 282 | - | ||

| 283 | - | ||

| 284 | -| Segment \# | Length (Bytes) | Speed | Direction | TXDATA FIFO | RXDATA FIFO | | ||

| 285 | -| :--------- | :------------- | :------- | :------------------ | :----------- | :---------------- | | ||

| 286 | -| 1 | 1 | standard | TX <br>qspi_d_io\[3:0\] | \[0\] 0x6B (ReadDataQuad) || | ||

| 287 | -| 2 | 3\* | quad | TX <br>qspi_d_io\[3:0\] | \[1\] Addr\[23:16\] <br>\[2\] Addr\[15:8\] <br>\[3\] Addr\[7:0\] || | ||

| 288 | -| 3 | 2 | N/A | None (Dummy) ||| | ||

| 289 | -| 4 | 1 | quad | RX <br>qspi_d_io\[3:0\] || \[0\] Data\[7:0\] | | ||

| 290 | - | ||

| 291 | - | ||

| 292 | -Note: In the preceding figure, segment 2 doesn’t show bytes 2 and 3 for brevity. | ||

| 293 | - | ||

| 294 | -#### Configuration | ||

| 295 | - | ||

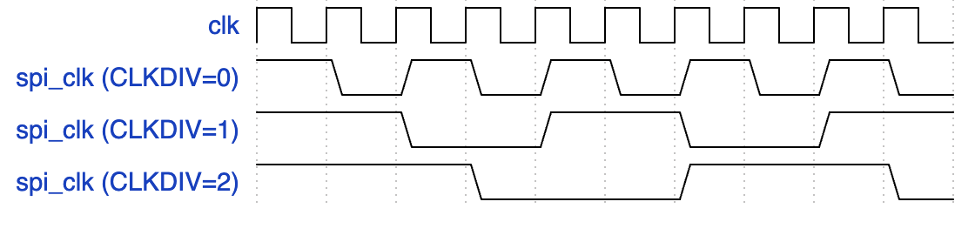

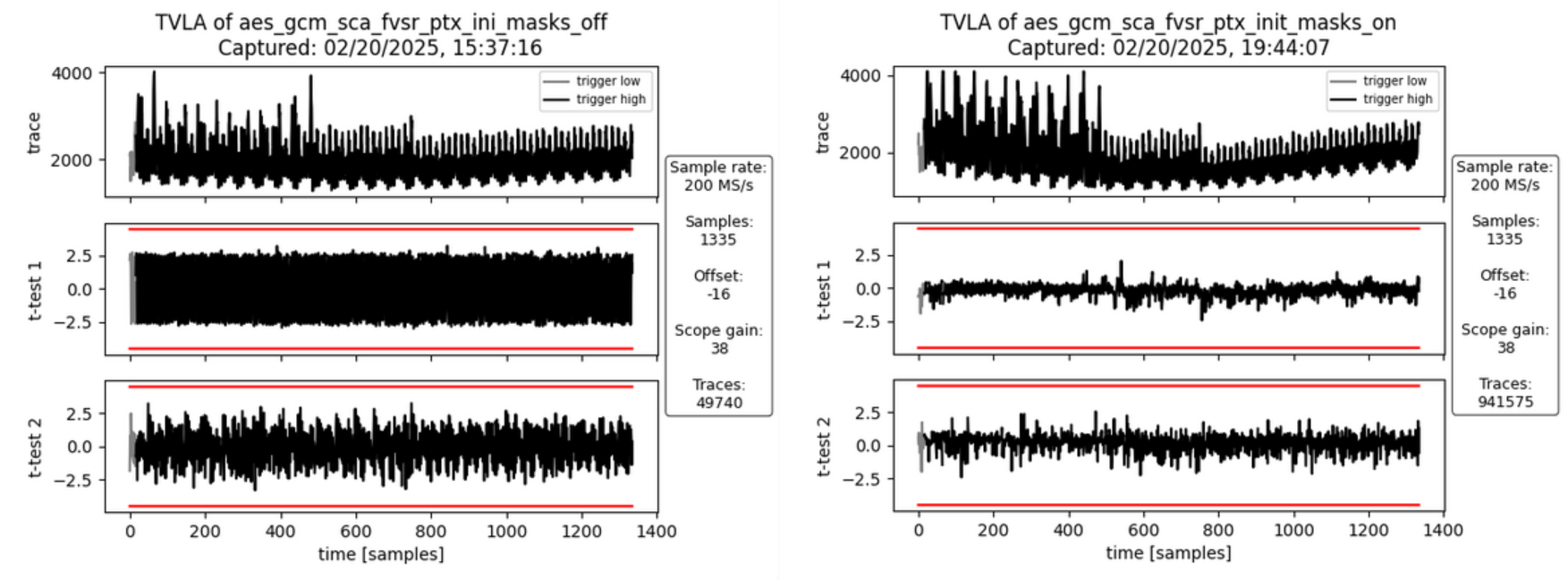

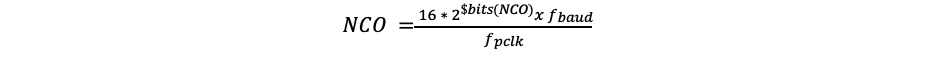

| 296 | -The CONFIGOPTS multi-register has one entry per CSB line and holds clock configuration and timing settings that are specific to each peripheral. After the CONFIGOPTS multi-register is programmed for each SPI peripheral device, the values can be left unchanged. | ||

| 297 | - | ||

| 298 | -The most common differences between target devices are the requirements for a specific SPI clock phase or polarity, CPOL and CPHA. These clock parameters can be set via the CONFIGOPTS.CPOL or CONFIGOPTS.CPHA register fields. | ||

| 299 | - | ||

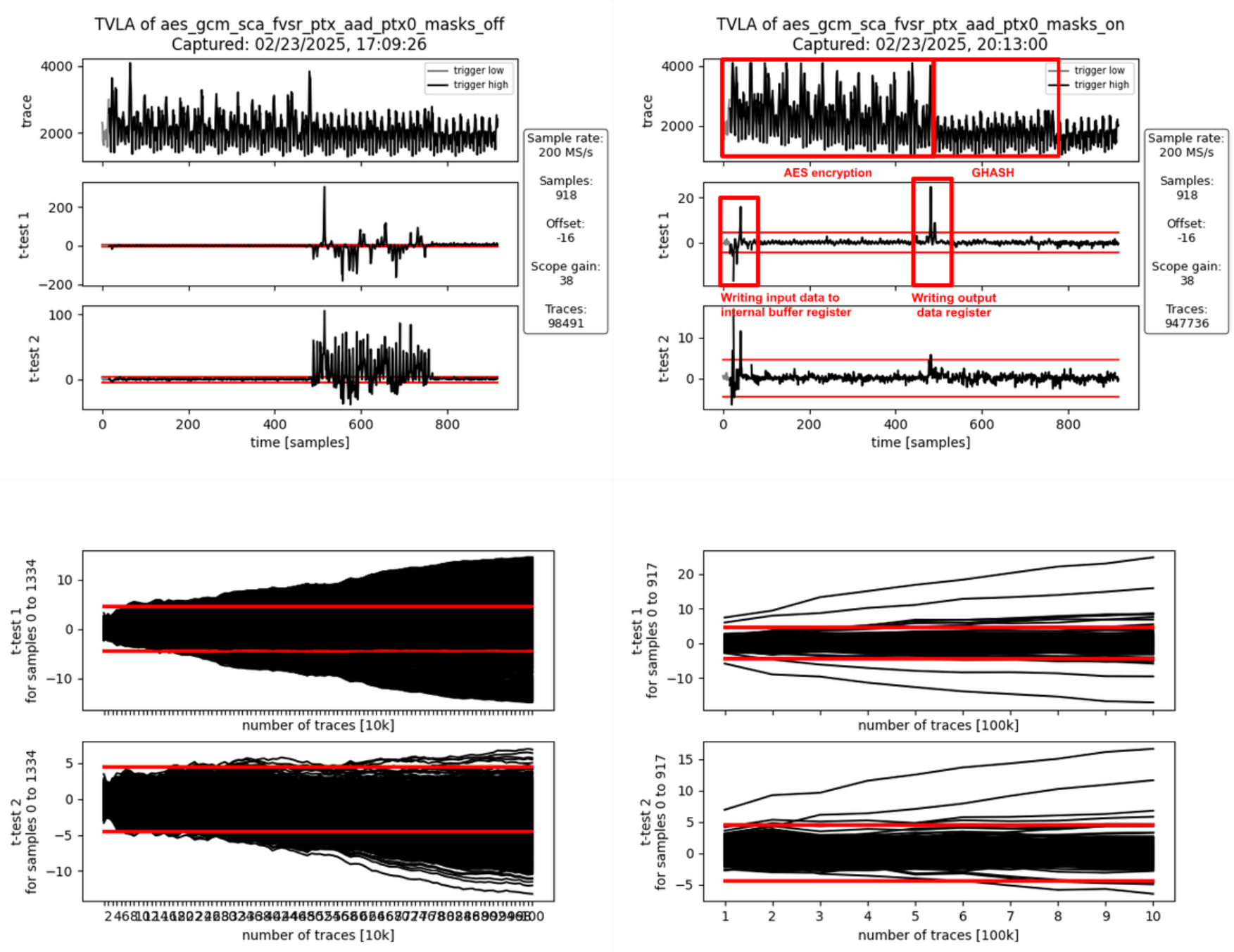

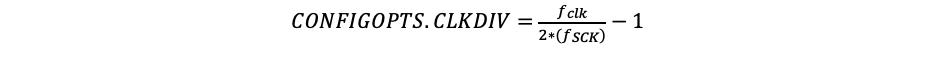

| 300 | -The SPI clock rate depends on the peripheral clock and a 16b clock divider configured by CONFIGOPTS.CLKDIV. The following equation is used to configure the SPI clock period: | ||

| 301 | - | ||

| 302 | - | ||

| 303 | - | ||

| 304 | -By default, CLKDIV is set to 0, which means that the maximum frequency that can be achieved is at most half the frequency of the peripheral clock (Fsck = Fclk/2). | ||

| 305 | - | ||

| 306 | -We can rearrange the equation to solve for the CLKDIV: | ||

| 307 | - | ||

| 308 | - | ||

| 309 | - | ||

| 310 | -Assuming a 400MHz target peripheral, and a SPI clock target of 100MHz: | ||

| 311 | - | ||

| 312 | -CONFIGOPTS.CLKDIV = (400/(2\*100)) -1 = 1 | ||

| 313 | - | ||

| 314 | -The following figure shows CONFIGOPTS. | ||

| 315 | - | ||

| 316 | -*Figure 7: CONFIGOPTS* | ||

| 317 | - | ||

| 318 | - | ||

| 319 | - | ||

| 320 | -#### Signal descriptions | ||

| 321 | - | ||

| 322 | -The QSPI block architecture inputs and outputs are described in the following table. | ||

| 323 | - | ||

| 324 | -| Name | Input or output | Description | | ||

| 325 | -| :------------------ | :-------------- | :-------------------------------------------------------- | | ||

| 326 | -| clk_i | input | All signal timings are related to the rising edge of clk. | | ||

| 327 | -| rst_ni | input | The reset signal is active LOW and resets the core. | | ||

| 328 | -| cio_sck_o | output | SPI clock | | ||

| 329 | -| cio_sck_en_o | output | SPI clock enable | | ||

| 330 | -| cio_csb_o\[1:0\] | output | Chip select \# (one hot, active low) | | ||

| 331 | -| cio_csb_en_o\[1:0\] | output | Chip select \# enable (one hot, active low) | | ||

| 332 | -| cio_csb_sd_o\[3:0\] | output | SPI data output | | ||

| 333 | -| cio_csb_sd_en_o | output | SPI data output enable | | ||

| 334 | -| cio_csb_sd_i\[3:0\] | input | SPI data input | | ||

| 335 | - | ||

| 336 | - | ||

| 337 | -#### SPI\_HOST IP programming guide | ||

| 338 | - | ||

| 339 | -The operation of the SPI\_HOST IP proceeds in seven general steps. | ||

| 340 | - | ||

| 341 | -To initialize the IP: | ||

| 342 | - | ||

| 343 | -1. Program the CONFIGOPTS multi-register with the appropriate timing and polarity settings for each csb line. | ||

| 344 | -2. Set the desired interrupt parameters. | ||

| 345 | -3. Enable the IP. | ||

| 346 | - | ||

| 347 | -Then for each command: | ||

| 348 | - | ||

| 349 | -4. Load the data to be transmitted into the FIFO using the TXDATA memory window. | ||

| 350 | -5. Specify the target device by programming the CSID. | ||

| 351 | -6. Specify the structure of the command by writing each segment into the COMMAND register. | ||

| 352 | - | ||

| 353 | - For multi-segment transactions, assert COMMAND.CSAAT for all but the last command segment. | ||

| 354 | - | ||

| 355 | -7. For transactions that expect to receive a reply, the data can then be read back from the RXDATA window. | ||

| 356 | - | ||

| 357 | -Steps 4-7 are then repeated for each subsequent command. | ||

| 358 | - | ||

| 359 | -### UART | ||

| 360 | - | ||

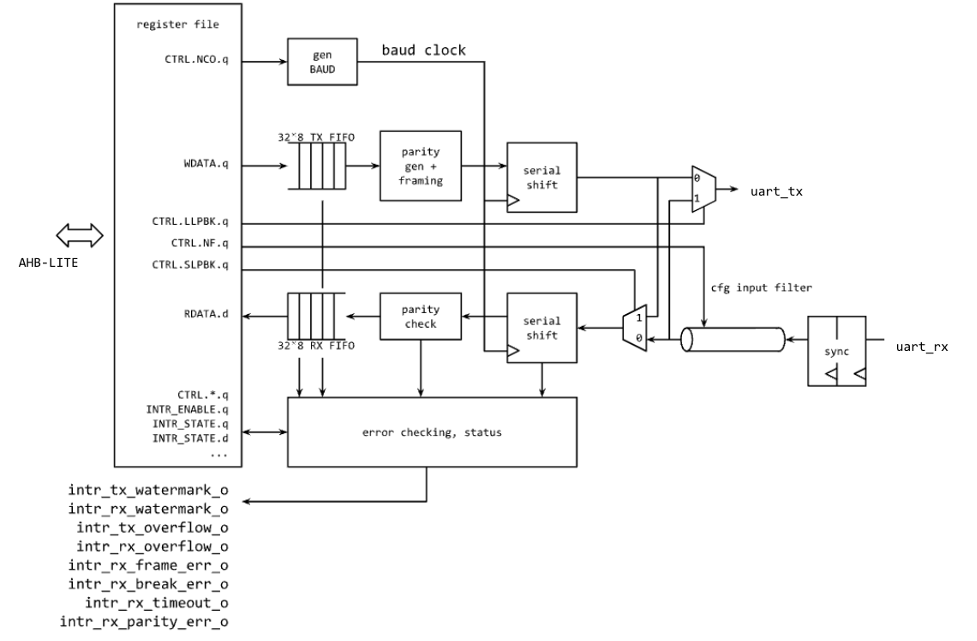

| 361 | -Caliptra implements a UART block that can communicate with a serial device that is accessible to FW over the AHB-lite Interface. This is a configuration that the SoC opts-in by defining CALIPTRA\_INTERNAL\_UART. | ||

| 362 | - | ||

| 363 | -The UART block is composed of the uart implementation. For information, see the [UART HWIP Technical Specification](https://opentitan.org/book/hw/ip/uart/). The design provides support for a programmable baud rate. The UART block is shown in the following figure. | ||

| 364 | - | ||

| 365 | -*Figure 8: UART block* | ||

| 366 | - | ||

| 367 | - | ||

| 368 | - | ||

| 369 | -#### Operation | ||

| 370 | - | ||

| 371 | -Transactions flow through the UART block starting with an AHB-lite write to WDATA, which triggers the transmit module to start a UART TX serial data transfer. The TX module dequeues the byte from the internal FIFO and shifts it out bit by bit at the baud rate. If TX is not enabled, the output is set high and WDATA in the FIFO is queued up. | ||

| 372 | - | ||

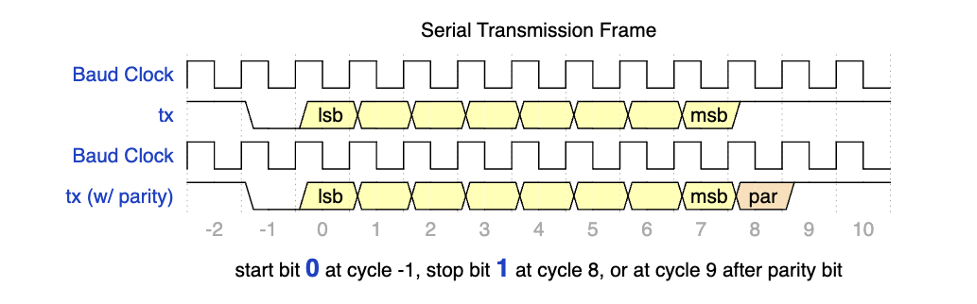

| 373 | -The following figure shows the transmit data on the serial lane, starting with the START bit, which is indicated by a high to low transition, followed by the 8 bits of data. | ||

| 374 | - | ||

| 375 | -*Figure 9: Serial transmission frame* | ||

| 376 | - | ||

| 377 | - | ||

| 378 | - | ||

| 379 | -On the receive side, after the START bit is detected, the data is sampled at the center of each data bit and stored into a FIFO. A user can monitor the FIFO status and read the data out of RDATA. | ||

| 380 | - | ||

| 381 | -#### Configuration | ||

| 382 | - | ||

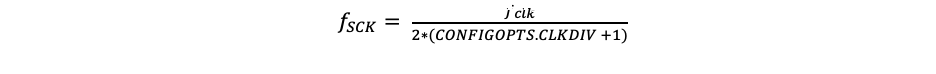

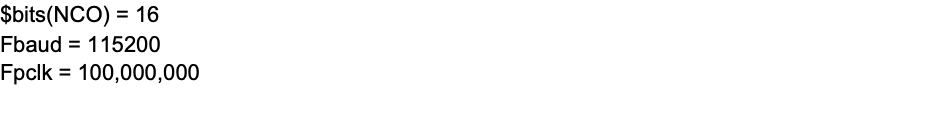

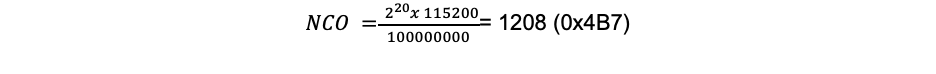

| 383 | -The baud rate can be configured using the CTRL.NCO register field. This should be set using the following equation: | ||

| 384 | - | ||

| 385 | - | ||

| 386 | - | ||

| 387 | -If the desired baud rate is 115,200bps: | ||

| 388 | - | ||

| 389 | - | ||

| 390 | - | ||

| 391 | - | ||

| 392 | - | ||

| 393 | -#### Signal descriptions | ||

| 394 | - | ||

| 395 | -The UART block architecture inputs and outputs are described in the following table. | ||

| 396 | - | ||

| 397 | -| Name | Input or output | Description | | ||

| 398 | -| :------- | :-------------- | :-------------------------------------------------------- | | ||

| 399 | -| clk_i | input | All signal timings are related to the rising edge of clk. | | ||

| 400 | -| rst_ni | input | The reset signal is active LOW and resets the core. | | ||

| 401 | -| cio_rx_i | input | Serial receive bit | | ||

| 402 | -| cio_tx_o | output | Serial transmit bit | | ||

| 403 | - | ||

| 404 | - | ||

| 405 | 260 | ## SoC mailbox | |

| 406 | 261 | ||

| 407 | 262 | For more information on the mailbox protocol, see [Mailbox](https://github.com/chipsalliance/caliptra-rtl/blob/main/docs/CaliptraIntegrationSpecification.md#mailbox) in the Caliptra Integration Specification. Mailbox registers accessible to the Caliptra microcontroller are defined in [internal-regs/mbox_csr](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.mbox_csr). | |

| 408 | 263 | ||

| 264 | +The RISC-V processor is able to access the SoC mailbox SRAM using a direct access mode (which bypasses the defined mailbox protocol). The addresses for performing this access are described in [SoC interface subsystem](#SoC-interface-subsystem) and in [mbox_sram](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.mbox_sram). In this mode, firmware must first acquire the mailbox lock. Then, reads and writes to the direct access address region will go directly to the SRAM block. Firmware must release the mailbox lock by writing to the [mbox_unlock](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.mbox_csr.mbox_unlock) register after direct access operations are completed. | ||

| 265 | + | ||

| 409 | 266 | ||

| 410 | 267 | ## Security state | |

| 411 | 268 | ||

| @@ -417,7 +274,7 @@ | |||

| 417 | 274 | ||

| 418 | 275 | * Caliptra JTAG is opened for the microcontroller and HW debug. | |

| 419 | 276 | ||

| 420 | -* Device secrets (UDS, FE, key vault, and obfuscation key) are programmed to debug values. | ||

| 277 | +* Device secrets (UDS, FE, key vault, csr hmac key and obfuscation key) are programmed to debug values. | ||

| 421 | 278 | ||

| 422 | 279 | If a transition to debug mode happens during ROM operation, any values computed from the use of device secrets may not match expected values. | |

| 423 | 280 | ||

| @@ -428,11 +285,14 @@ | |||

| 428 | 285 | | Name | Default value | | |

| 429 | 286 | | :-------------------------- | :------------ | | |

| 430 | 287 | | Obfuscation Key Debug Value | All 0x1 | | |

| 288 | +| CSR HMAC Key Debug Value | All 0x1 | | ||

| 431 | 289 | | UDS Debug Value | All 0x1 | | |

| 432 | 290 | | Field Entropy Debug Value | All 0x1 | | |

| 433 | 291 | | Key Vault Debug Value 0 | All 0xA | | |

| 434 | 292 | | Key Vault Debug Value 1 | All 0x5 | | |

| 435 | 293 | ||

| 294 | + | ||

| 295 | +Note: When entering debug or scan mode, all crypto engines are zeroized. Before starting any crypto operation in these modes, the status registers of all crypto engines must be checked to confirm they are ready. Failing to do so may trigger a fatal error caused by concurrent crypto operations. | ||

| 436 | 296 | ||

| 437 | 297 | ## Clock gating | |

| 438 | 298 | ||

| @@ -472,17 +332,17 @@ | |||

| 472 | 332 | ||

| 473 | 333 | * JTAG accesses | |

| 474 | 334 | ||

| 475 | -* APB transactions | ||

| 476 | - | ||

| 477 | -Activity on the APB interface only wakes up the SoC IFC clock. All other clocks remain off until any other condition is met or the core exits the halt state. | ||

| 478 | - | ||

| 479 | -| Cpu_halt_status | PSEL | Generic input wires <br>|| fatal error <br>|| debug/scan mode <br> ||JTAG access | Expected behavior | | ||

| 335 | +* AXI transactions | ||

| 336 | + | ||

| 337 | +Activity on the AXI subordinate interface only wakes up the SoC IFC clock. All other clocks remain off until any other condition is met or the core exits the halt state. | ||

| 338 | + | ||

| 339 | +| Cpu_halt_status | s_axi_active | Generic input wires <br>|| fatal error <br>|| debug/scan mode <br> ||JTAG access | Expected behavior | | ||

| 480 | 340 | | :-------------- | :--- | :---------- | :-------------- | | |

| 481 | 341 | | 0 | X | X | All gated clocks active | | |

| 482 | 342 | | 1 | 0 | 0 | All gated clocks inactive | | |

| 483 | 343 | | 1 | 0 | 1 | All gated clocks active (as long as condition is true) | | |

| 484 | -| 1 | 1 | 0 | Soc_ifc_clk_cg active (as long as PSEL = 1) <br>All other clks inactive | | ||

| 485 | -| 1 | 1 | 1 | Soc_ifc_clk_cg active (as long as condition is true OR PSEL = 1) <br>All other clks active (as long as condition is true) | | ||

| 344 | +| 1 | 1 | 0 | Soc_ifc_clk_cg active (as long as s_axi_active = 1) <br>All other clks inactive | | ||

| 345 | +| 1 | 1 | 1 | Soc_ifc_clk_cg active (as long as condition is true OR s_axi_active = 1) <br>All other clks active (as long as condition is true) | | ||

| 486 | 346 | ||

| 487 | 347 | ||

| 488 | 348 | ### Usage | |

| @@ -490,7 +350,7 @@ | |||

| 490 | 350 | The following applies to the clock gating feature: | |

| 491 | 351 | ||

| 492 | 352 | * The core should only be halted after all pending vault writes are done and cryptographic operations are complete. | |

| 493 | -* While the core is halted, any APB transaction wakes up the SoC interface clock and leaves all other clocks disabled. If the core is still halted when the APB transactions are done, the SoC interface clock is returned to a disabled state. . | ||

| 353 | +* While the core is halted, any AXI transaction wakes up the SoC interface clock and leaves all other clocks disabled. If the core is still halted when the AXI transactions are done, the SoC interface clock is returned to a disabled state. . | ||

| 494 | 354 | * The RDC clock is similar to an ungated clock and is only disabled when a reset event occurs. This avoids metastability on flops. The RDC clock operates independently of core halt status. | |

| 495 | 355 | ||

| 496 | 356 | ||

| @@ -530,7 +390,7 @@ | |||

| 530 | 390 | ||

| 531 | 391 | ### Operation | |

| 532 | 392 | ||

| 533 | -Requests for entropy bits start with [command requests](https://opentitan.org/book/hw/ip/csrng/doc/theory_of_operation.html#general-command-format) over the AHB-lite interface to the csrng [CMD\_REQ](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.csrng_reg.CMD_REQ) register. | ||

| 393 | +Requests for entropy bits start with [command requests](https://opentitan.org/book/hw/ip/csrng/doc/theory_of_operation.html#general-command-format) over the AHB-lite interface to the csrng [CMD\_REQ](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.csrng_reg.CMD_REQ) register. | ||

| 534 | 394 | ||

| 535 | 395 | The following describes the fields of the command request header: | |

| 536 | 396 | ||

| @@ -542,7 +402,7 @@ | |||

| 542 | 402 | ||

| 543 | 403 | * Generate Length: Only defined for the generate command, this field is the total number of cryptographic entropy blocks requested. Each unit represents 128 bits of entropy returned. A value of 8 would return a total of 1024 bits. The maximum size supported is 4096. | |

| 544 | 404 | ||

| 545 | -First an instantiate command is requested over the SW application interface to initialize an instance in the CSRNG module. Depending on the flag0 and clen fields in the command header, a request to the entropy\_src module over the entropy interface is sent to seed the csrng. This can take a few milliseconds if the seed entropy is not immediately available. | ||

| 405 | +First an instantiate command is requested over the SW application interface to initialize an instance in the CSRNG module. Depending on the flag0 and clen fields in the command header, a request to the entropy\_src module over the entropy interface is sent to seed the csrng. This can take a few milliseconds if the seed entropy is not immediately available. | ||

| 546 | 406 | ||

| 547 | 407 | Example instantiation: | |

| 548 | 408 | ||

| @@ -560,7 +420,7 @@ | |||

| 560 | 420 | | T | 1-12 | Only provided additional data is used as seed. | | |

| 561 | 421 | ||

| 562 | 422 | ||

| 563 | -Next a generate command is used to request generation of cryptographic entropy bits. The glen field defines how many 128 bit words are to be returned to the application interface. After the generated bits are ready, they can be read out via the GENBITS register. This register must be read out glen \* 4 times for each request made. | ||

| 423 | +Next a generate command is used to request generation of cryptographic entropy bits. The glen field defines how many 128 bit words are to be returned to the application interface. After the generated bits are ready, they can be read out via the GENBITS register. This register must be read out glen \* 4 times for each request made. | ||

| 564 | 424 | ||

| 565 | 425 | Example generate command: | |

| 566 | 426 | ||

| @@ -634,6 +494,111 @@ | |||

| 634 | 494 | ||

| 635 | 495 | The CSRNG may only be enabled if entropy\_src is enabled. After it is disabled, CSRNG may only be re-enabled after entropy\_src has been disabled and re-enabled. | |

| 636 | 496 | ||

| 497 | +### FIPS considerations | ||

| 498 | + | ||

| 499 | +The following sections illustrate the self-test parameter configuration. The | ||

| 500 | +`entropy_src` block provides additional tests, but Caliptra focuses primarily | ||

| 501 | +on the adaptive and repetition count tests, which are the ones strictly | ||

| 502 | +required for FIPS compliance. Additional details can be found in NIST | ||

| 503 | +publication SP 800-90B. | ||

| 504 | + | ||

| 505 | +The TRNG must be re-initialized whenever self-test parameter changes are | ||

| 506 | +needed. As described in the previous section, the initialization steps | ||

| 507 | +are as follows: | ||

| 508 | + | ||

| 509 | +1. Disable `csrng` and `entropy_src` in that order. | ||

| 510 | +2. Apply new self-test configuration. | ||

| 511 | +3. Enable `entropy_src` and `csrng` in that order. | ||

| 512 | + | ||

| 513 | +### Adaptive self-test window and thresholds | ||

| 514 | + | ||

| 515 | +This section details the configuration of the `entropy_src`, focusing on how | ||

| 516 | +the test window size for the adaptive self-test is determined and how it | ||

| 517 | +relates to threshold calculations. | ||

| 518 | + | ||

| 519 | +#### Understanding Test Window Sizes | ||

| 520 | + | ||

| 521 | +The adaptive self-test within the `entropy_src` block utilizes a | ||

| 522 | +configurable test window. To clarify its interpretation, two terms are | ||

| 523 | +defined: | ||

| 524 | + | ||

| 525 | +* `ENTROPY_TEST_WINDOW`: This refers to the test window size directly | ||

| 526 | + configured in the hardware registers of the `entropy_src` block. | ||

| 527 | +* `ACTUAL_TEST_WINDOW`: This refers to the effective window size used for | ||

| 528 | + the adaptive self-test threshold calculations. Its value depends on how | ||

| 529 | + the test scores are aggregated. | ||

| 530 | + | ||

| 531 | +The aggregation method is determined by the CONF.THRESHOLD_SCOPE setting in | ||

| 532 | +the entropy_src block. | ||

| 533 | + | ||

| 534 | +#### Aggregate per symbol | ||

| 535 | + | ||

| 536 | +When CONF.THRESHOLD_SCOPE is enabled: | ||

| 537 | + | ||

| 538 | +* The adaptive test combines the inputs from all physical entropy lines | ||

| 539 | + into a single, cumulative score. | ||

| 540 | +* The test essentially treats the combined input as a single binary stream, | ||

| 541 | + counting the occurrences of '1's. | ||

| 542 | +* In this configuration: | ||

| 543 | + * If `ENTROPY_TEST_WINDOW` is set to 1024, then | ||

| 544 | + * `ACTUAL_TEST_WINDOW` = `ENTROPY_TEST_WINDOW` = 1024 | ||

| 545 | + | ||

| 546 | +#### Handle each physical noise source separately | ||

| 547 | + | ||

| 548 | +When `CONF.THRESHOLD_SCOPE` is disabled: | ||

| 549 | + | ||

| 550 | +* The adaptive test scores each individual physical noise input line | ||

| 551 | + independently. | ||

| 552 | +* This allows for monitoring the health of each noise source. | ||

| 553 | +* In this configuration (assuming, for example, 4 noise sources): | ||

| 554 | + * If `ENTROPY_TEST_WINDOW` is set to 4096 bits, then | ||

| 555 | + * `ACTUAL_TEST_WINDOW` = (`ENTROPY_TEST_WINDOW` / 4) = 1024 | ||

| 556 | + | ||

| 557 | +#### Configuring adaptive self-test thresholds | ||

| 558 | + | ||

| 559 | +Once the `ACTUAL_TEST_WINDOW` is determined, the adaptive self-test | ||

| 560 | +thresholds can be configured as follows: | ||

| 561 | + | ||

| 562 | +* `ADAPTP_HI_THRESHOLDS.FIPS_THRESH` = `adaptp_cutoff` | ||

| 563 | +* `ADAPTP_LO_THRESHOLDS.FIPS_THRESH` = `ACTUAL_TEST_WINDOW` - `adaptp_cutoff` | ||

| 564 | + | ||

| 565 | +Here, `adaptp_cutoff` represents the pre-determined cutoff value for the | ||

| 566 | +adaptive proportion test, as defined by NIST SP 800-90B. See the threshold | ||

| 567 | +calculations below as an example. | ||

| 568 | + | ||

| 569 | +\\(α = 2^{-40}\\) (recommended)\ | ||

| 570 | +\\(H = 0.5\\) (example, estimated entropy measured from hardware)\ | ||

| 571 | +\\(W\\) = `ACTUAL_TEST_WINDOW`\ | ||

| 572 | +`adaptp_cutoff` = \\(1 + critbinom(W, 2^{-H}, 1 - α)\\) | ||

| 573 | + | ||

| 574 | +> Note: The `critbinom` function (critical binomial distribution function) is | ||

| 575 | +> implemented by most spreadsheet applications. | ||

| 576 | + | ||

| 577 | +### Recommended configuration | ||

| 578 | + | ||

| 579 | +The following configuration is recommended for the adaptive and repetition | ||

| 580 | +count tests: | ||

| 581 | + | ||

| 582 | +#### Adaptive test | ||

| 583 | + | ||

| 584 | +1. Set `CONF.THRESHOLD_SCOPE` to disabled. This allows the test to monitor | ||

| 585 | + and score each physical noise source individually, providing more granular | ||

| 586 | + health information. | ||

| 587 | +2. Set `HEALTH_TEST_WINDOWS.FIPS_WINDOW` to 4096 bits. This value serves | ||

| 588 | + as the `ENTROPY_TEST_WINDOW`. With the current 4 noise source configuration, | ||

| 589 | + this is equivalent to 1024 bits per noise source, where each source produces | ||

| 590 | + 1 bit of entropy as defined in NIST SP 800-90B. | ||

| 591 | +3. Calculate thresholds. Use an `ACTUAL_TEST_WINDOW` of 1024 bits (derived | ||

| 592 | + from step 2) in the adaptive test threshold formulas provided earlier in | ||

| 593 | + this subsection. | ||

| 594 | + | ||

| 595 | +#### Repetition count test | ||

| 596 | + | ||

| 597 | +The methodology used for calculating the repetition count threshold in the | ||

| 598 | +ROM boot phase can be directly applied for this test as well. The threshold is | ||

| 599 | +applied on a per-noise-source basis. | ||

| 600 | + | ||

| 601 | + | ||

| 637 | 602 | ## External-TRNG REQ HW API | |

| 638 | 603 | ||

| 639 | 604 | For SoCs that choose to not instantiate Caliptra’s integrated TRNG, Caliptra provides a TRNGREQ HW API. | |

| @@ -647,18 +612,16 @@ | |||

| 647 | 612 | ||

| 648 | 613 | ## SoC-SHA accelerator HW API | |

| 649 | 614 | ||

| 650 | -Caliptra provides a SHA accelerator HW API for SoC and Caliptra internal FW to use. It is atomic in nature in that only one of them can use the SHA accelerator HW API at the same time. Details of the SHA accelerator register block may be found in the GitHub repository in [documentation](https://chipsalliance.github.io/caliptra-rtl/main/external-regs/?p=caliptra_top_reg.sha512_acc_csr) generated from the register definition file. | ||

| 615 | +Caliptra provides a SHA accelerator HW API for Caliptra internal FW to use via mailbox or via DMA operations through the AXI subordinate interface. The SHA accelerator HW API is restricted on AXI for use by Caliptra via the AXI DMA assist block; this access restriction is enforced by checking logic on the AXI AxUSER signal associated with the request. | ||

| 651 | 616 | ||

| 652 | 617 | Using the HW API: | |

| 653 | 618 | ||

| 654 | 619 | * A user of the HW API first locks the accelerator by reading the LOCK register. A read that returns the value 0 indicates that the resource was locked for exclusive use by the requesting user. A write of ‘1 clears the lock. | |

| 655 | -* The USER register captures the APB pauser value of the requestor that locked the SHA accelerator. This is the only user that is allowed to control the SHA accelerator by performing APB register writes. Writes by any other agent on the APB interface are dropped. | ||

| 656 | -* MODE register is written to set the SHA execution mode. | ||

| 657 | - * SHA accelerator supports both SHA384 and SHA512 modes of operation. | ||

| 658 | - * SHA supports **streaming** mode: SHA is computed on a stream of incoming data to the DATAIN register. The EXECUTE register, when set, indicates to the accelerator that streaming is complete. The accelerator can then publish the result into the DIGEST register. When the VALID bit of the STATUS register is set, then the result in the DIGEST register is valid. | ||

| 659 | - * SHA supports **Mailbox** mode: SHA is computed on LENGTH (DLEN) bytes of data stored in the mailbox beginning at START\_ADDRESS. This computation is performed when the EXECUTE register is set by the user. When the operation is completed and the result in the DIGEST register is valid, SHA accelerator sets the VALID bit of the STATUS register. | ||

| 660 | - * The SHA computation engine in the SHA accelerator requires big endian data, but the SHA accelerator can accommodate mailbox input data in either the little endian or big endian format. By default, input data is assumed to be little endian and is swizzled to big endian at the byte level prior to computation. For the big endian format, data is loaded into the SHA engine as-is. Users may configure the SHA accelerator to treat data as big endian by setting the ENDIAN\_TOGGLE bit appropriately. | ||

| 661 | - * See the register definition for the encodings. | ||

| 620 | +* The USER register captures the AXI USERID value of the requestor that locked the SHA accelerator. This is the only user that is allowed to control the SHA accelerator by performing AXI register writes. Writes by any other agent on the AXI subordinate interface are dropped. | ||

| 621 | +* SHA supports **Mailbox** mode: SHA is computed on LENGTH (DLEN) bytes of data stored in the mailbox beginning at START\_ADDRESS. This computation is performed when the EXECUTE register is set by the user. When the operation is completed and the result in the DIGEST register is valid, SHA accelerator sets the VALID bit of the STATUS register. | ||

| 622 | +* Note that even though the mailbox size is fixed, due to SHA save/restore function enhancement, there is no limit on the size of the block that needs to be SHAd. SOC needs to follow FW API | ||

| 623 | +* The SHA computation engine in the SHA accelerator requires big endian data, but the SHA accelerator can accommodate mailbox input data in either the little endian or big endian format. By default, input data is assumed to be little endian and is swizzled to big endian at the byte level prior to computation. For the big endian format, data is loaded into the SHA engine as-is. Users may configure the SHA accelerator to treat data as big endian by setting the ENDIAN\_TOGGLE bit appropriately. | ||

| 624 | +* See the register definition for the encodings. | ||

| 662 | 625 | * SHA engine also provides a ‘zeroize’ function through its CONTROL register to clear any of the SHA internal state. This can be used when the user wants to conceal previous state for debug or security reasons. | |

| 663 | 626 | ||

| 664 | 627 | ## JTAG implementation | |

| @@ -683,7 +646,7 @@ | |||

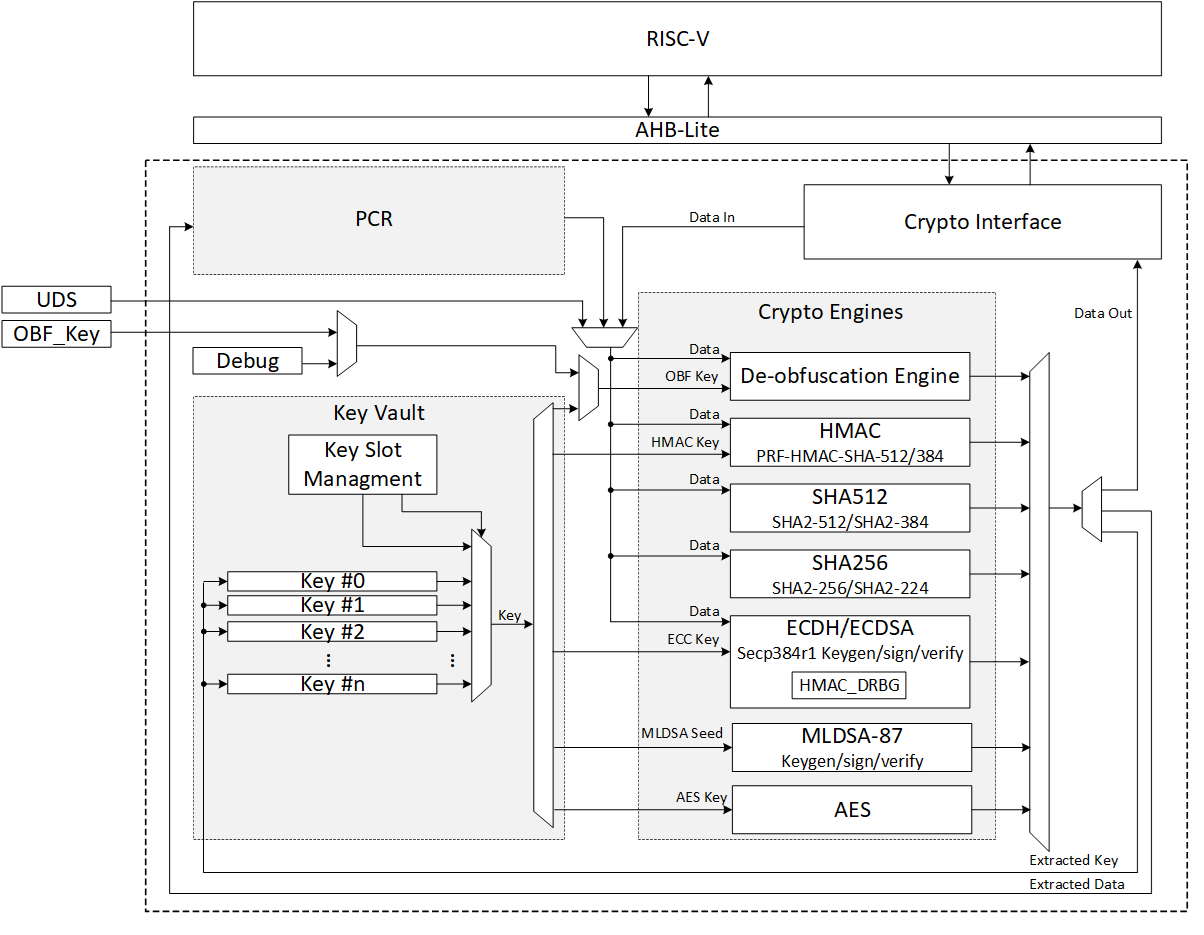

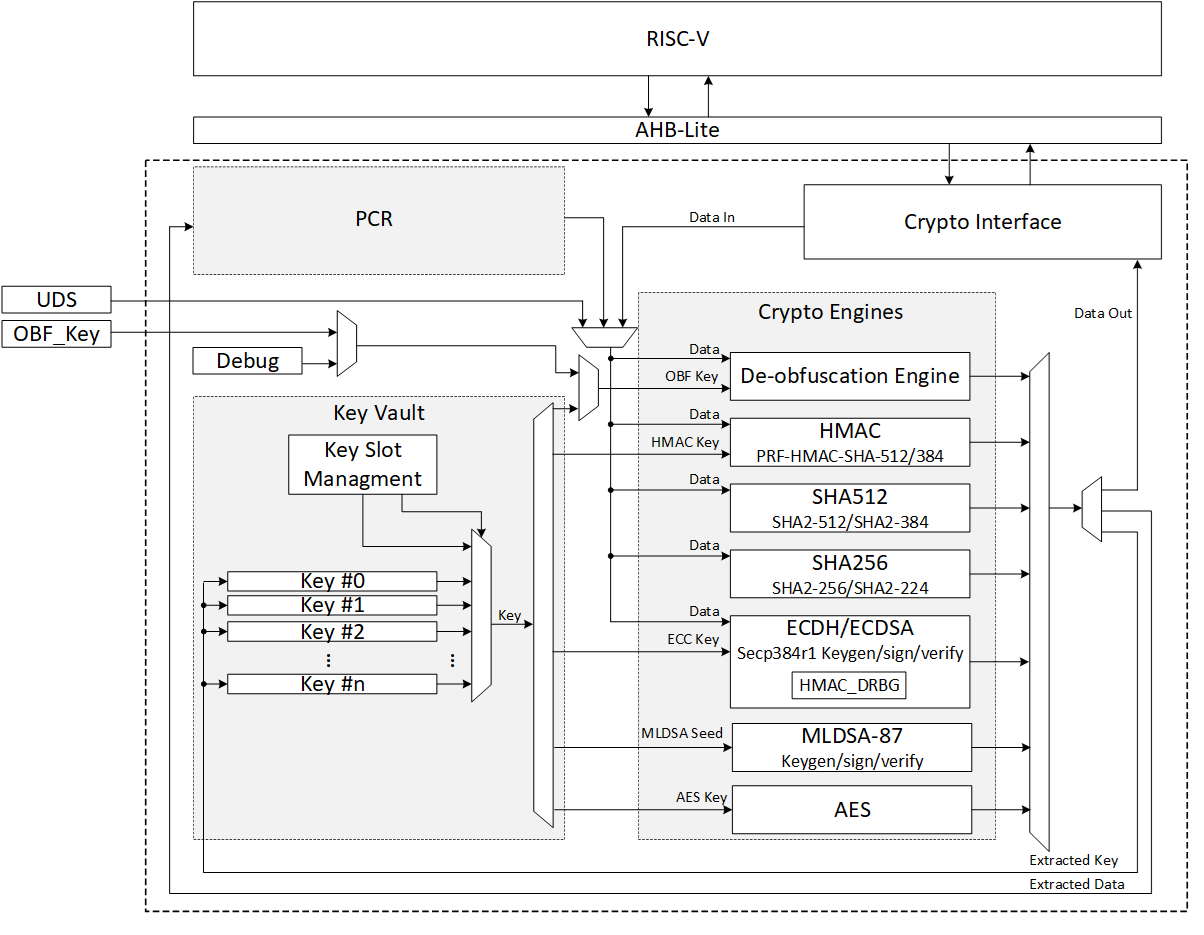

| 683 | 646 | * De-obfuscation engine | |

| 684 | 647 | * SHA512/384 (based on NIST FIPS 180-4 [2]) | |

| 685 | 648 | * SHA256 (based on NIST FIPS 180-4 [2]) | |

| 686 | - * HMAC384 (based on [NIST FIPS 198-1](https://nvlpubs.nist.gov/nistpubs/FIPS/NIST.FIPS.198-1.pdf) [5] and [RFC 4868](https://tools.ietf.org/html/rfc4868) [6]) | ||

| 649 | + * HMAC512 (based on [NIST FIPS 198-1](https://nvlpubs.nist.gov/nistpubs/FIPS/NIST.FIPS.198-1.pdf) [5] and [RFC 4868](https://tools.ietf.org/html/rfc4868) [6]) | ||

| 687 | 650 | * Public-key cryptography | |

| 688 | 651 | * NIST Secp384r1 Deterministic Digital Signature Algorithm (based on FIPS-186-4 [11] and RFC 6979 [7]) | |

| 689 | 652 | * Key vault | |

| @@ -694,7 +657,7 @@ | |||

| 694 | 657 | ||

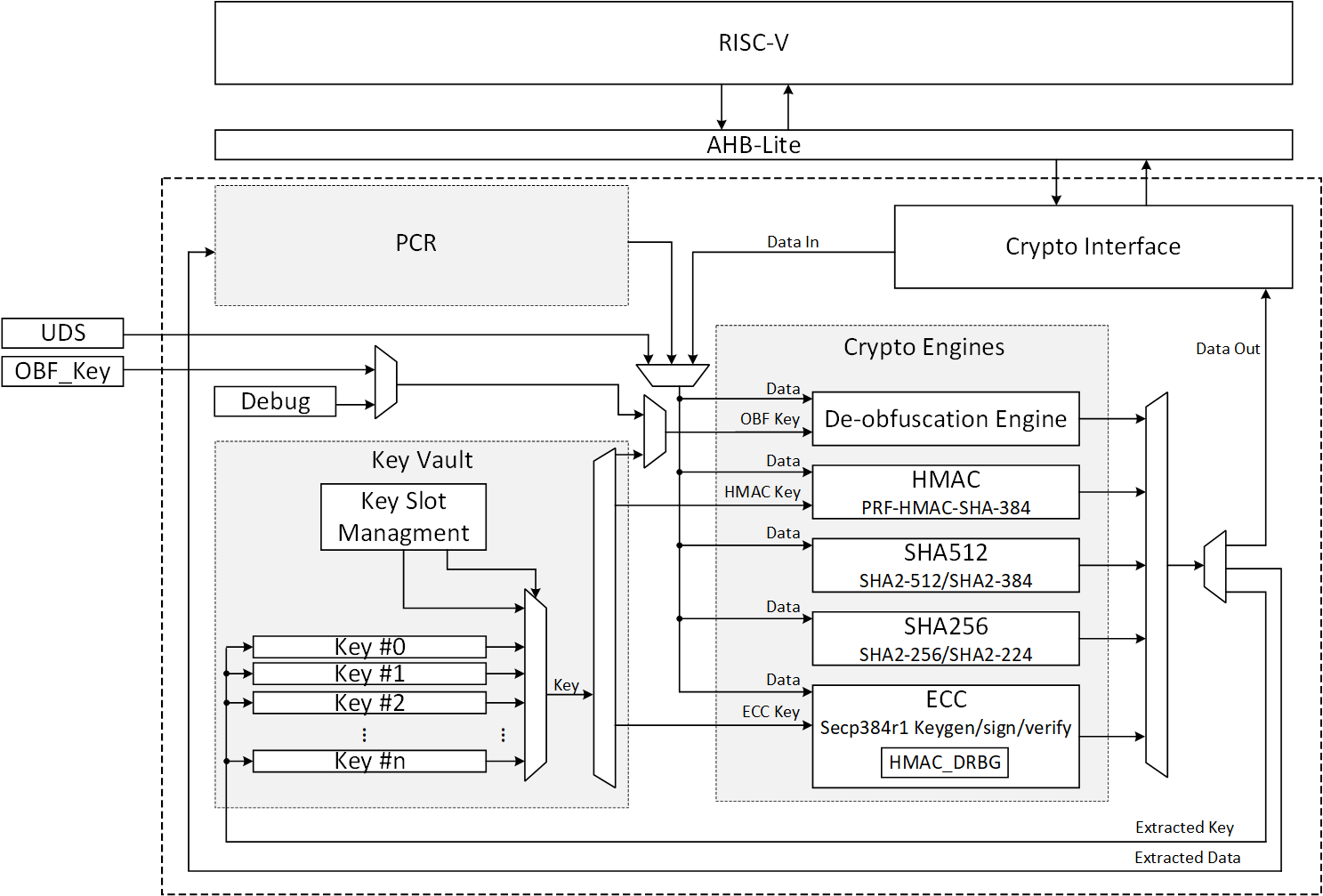

| 695 | 658 | *Figure 17: Caliptra cryptographic subsystem* | |

| 696 | 659 | ||

| 697 | - | ||

| 660 | + | ||

| 698 | 661 | ||

| 699 | 662 | ## SHA512/SHA384 | |

| 700 | 663 | ||

| @@ -927,13 +890,13 @@ | |||

| 927 | 890 | | 1 KiB message | 8761 | 21.90 | 45,657 | | |

| 928 | 891 | ||

| 929 | 892 | ||

| 930 | -## HMAC384 | ||

| 931 | - | ||

| 932 | -Hash-based message authentication code (HMAC) is a cryptographic authentication technique that uses a hash function and a secret key. HMAC involves a cryptographic hash function and a secret cryptographic key. This implementation supports HMAC-SHA-384-192 as specified in [NIST FIPS 198-1](https://nvlpubs.nist.gov/nistpubs/FIPS/NIST.FIPS.198-1.pdf) [5]. The implementation is compatible with the HMAC-SHA-384-192 authentication and integrity functions defined in [RFC 4868](https://tools.ietf.org/html/rfc4868) [6]. | ||

| 933 | - | ||

| 934 | -Caliptra HMAC implementation uses SHA384 as the hash function, accepts a 384-bit key, and generates a 384-bit tag. | ||

| 935 | - | ||

| 936 | -The implementation also supports PRF-HMAC-SHA-384. The PRF-HMAC-SHA-384 algorithm is identical to HMAC-SHA-384-192, except that variable-length keys are permitted, and the truncation step is not performed. | ||

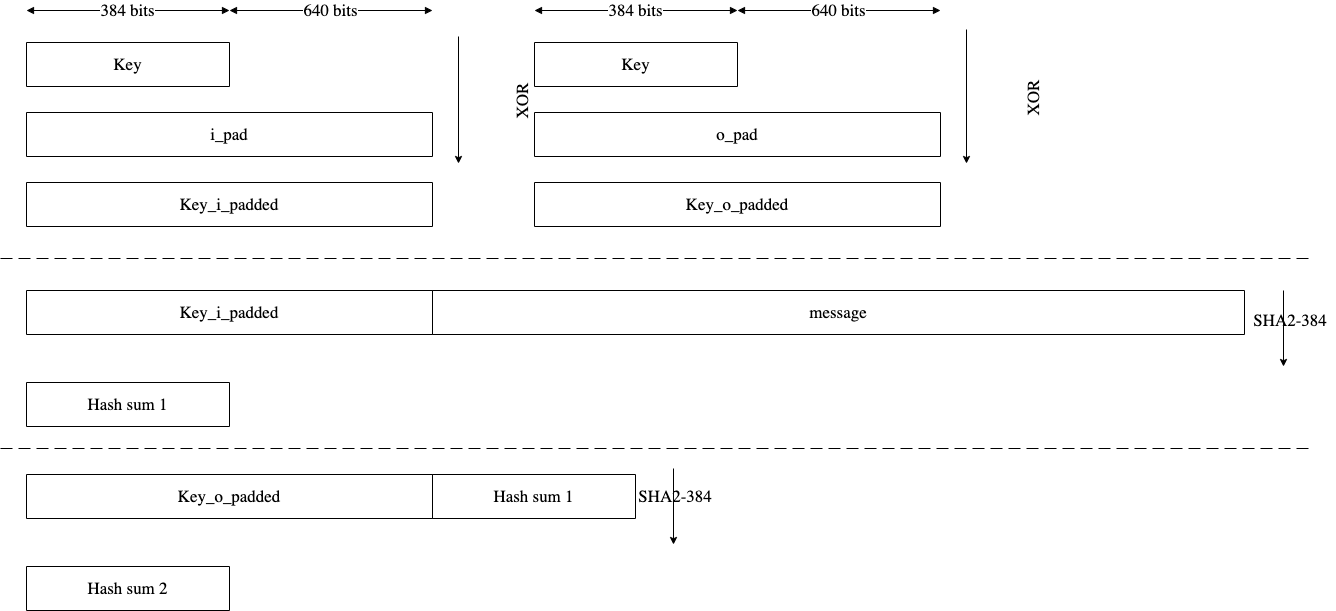

| 893 | +## HMAC512/HMAC384 | ||

| 894 | + | ||

| 895 | +Hash-based message authentication code (HMAC) is a cryptographic authentication technique that uses a hash function and a secret key. HMAC involves a cryptographic hash function and a secret cryptographic key. This implementation supports the HMAC512 variants HMAC-SHA-512-256 and HMAC-SHA-384-192 as specified in [NIST FIPS 198-1](https://nvlpubs.nist.gov/nistpubs/FIPS/NIST.FIPS.198-1.pdf) [5]. The implementation is compatible with the HMAC-SHA-512-256 and HMAC-SHA-384-192 authentication and integrity functions defined in [RFC 4868](https://tools.ietf.org/html/rfc4868) [6]. | ||

| 896 | + | ||

| 897 | +Caliptra HMAC implementation uses SHA512 as the hash function, accepts a 512-bit key, and generates a 512-bit tag. | ||

| 898 | + | ||

| 899 | +The implementation also supports PRF-HMAC-SHA-512. The PRF-HMAC-SHA-512 algorithm is identical to HMAC-SHA-512-256, except that variable-length keys are permitted, and the truncation step is not performed. | ||

| 937 | 900 | ||

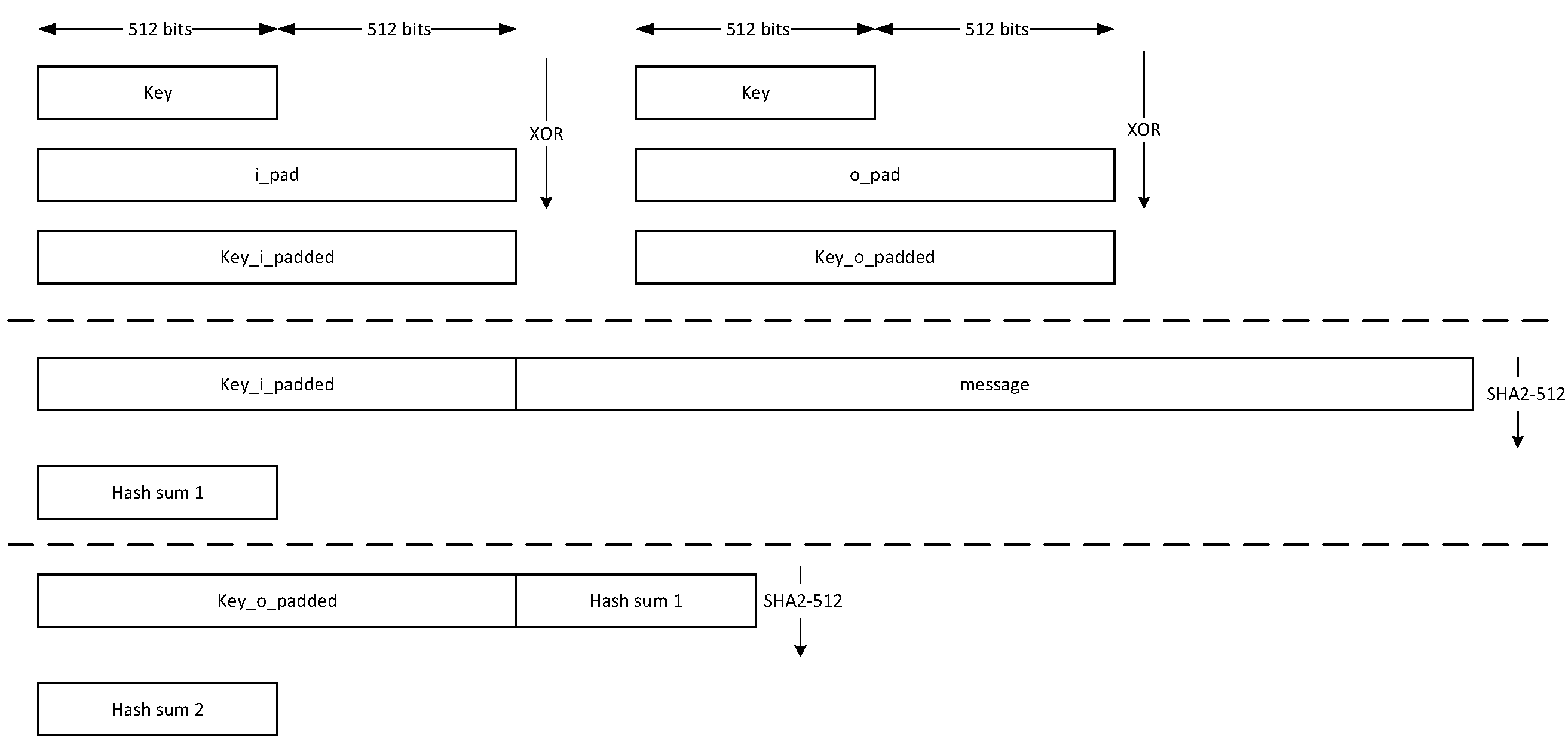

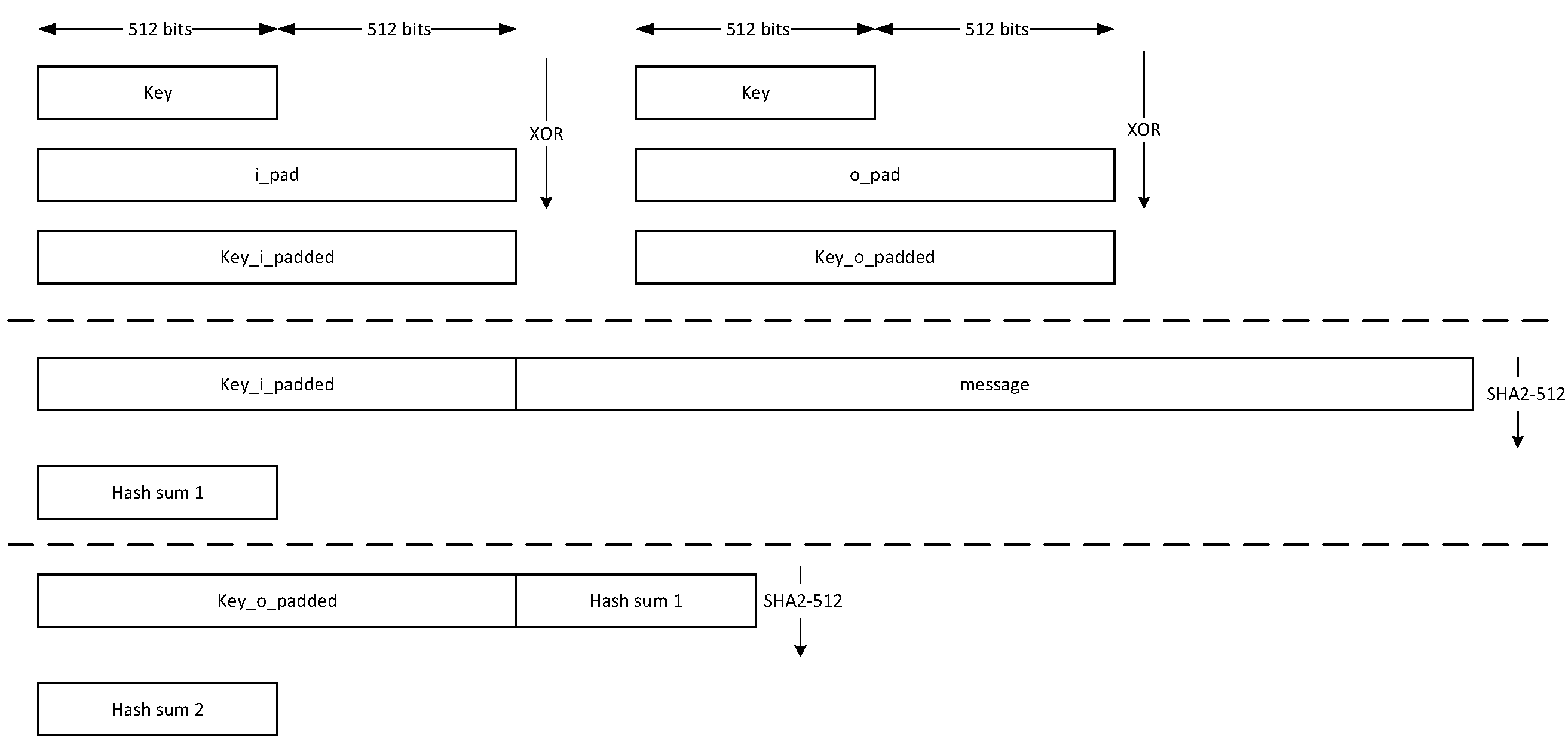

| 938 | 901 | The HMAC algorithm is described as follows: | |

| 939 | 902 | * The key is fed to the HMAC core to be padded | |

| @@ -980,9 +943,15 @@ | |||

| 980 | 943 | ||

| 981 | 944 | #### Hashing | |

| 982 | 945 | ||

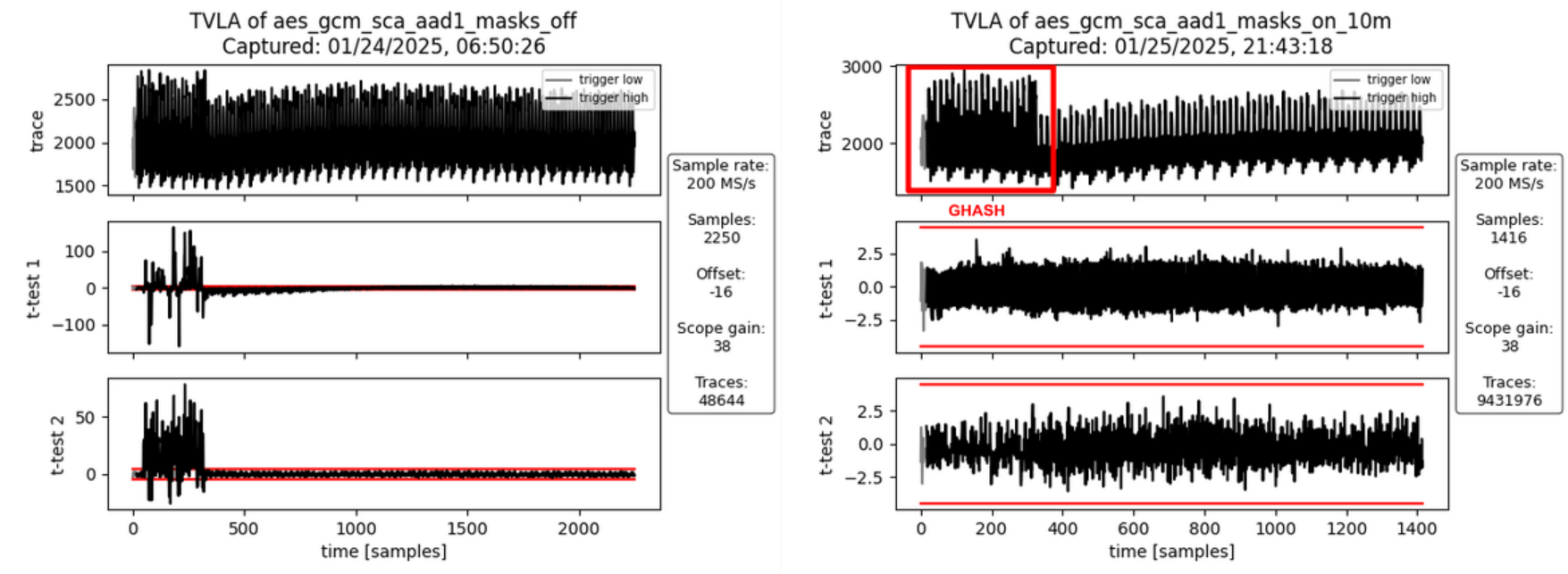

| 983 | -The HMAC core performs the sha2-384 function to process the hash value of the given message. The algorithm processes each block of the 1024 bits from the message, using the result from the previous block. This data flow is shown in the following figure. | ||

| 984 | - | ||

| 985 | -*Figure 28: HMAC-SHA-384-192 data flow* | ||

| 946 | +The HMAC512 core performs the sha2-512 function to process the hash value of the given message. The algorithm processes each block of the 1024 bits from the message, using the result from the previous block. This data flow is shown in the following figure. | ||

| 947 | + | ||

| 948 | +*Figure 28: HMAC-SHA-512-256 data flow* | ||

| 949 | + | ||

| 950 | + | ||

| 951 | + | ||

| 952 | +The HMAC384 core performs the sha2-384 function to process the hash value of the given message. The algorithm processes each block of the 1024 bits from the message, using the result from the previous block. This data flow is shown in the following figure. | ||

| 953 | + | ||

| 954 | +*Figure 29: HMAC-SHA-384-192 data flow* | ||

| 986 | 955 | ||

| 987 | 956 |  | |

| 988 | 957 | ||

| @@ -990,26 +959,33 @@ | |||

| 990 | 959 | ||

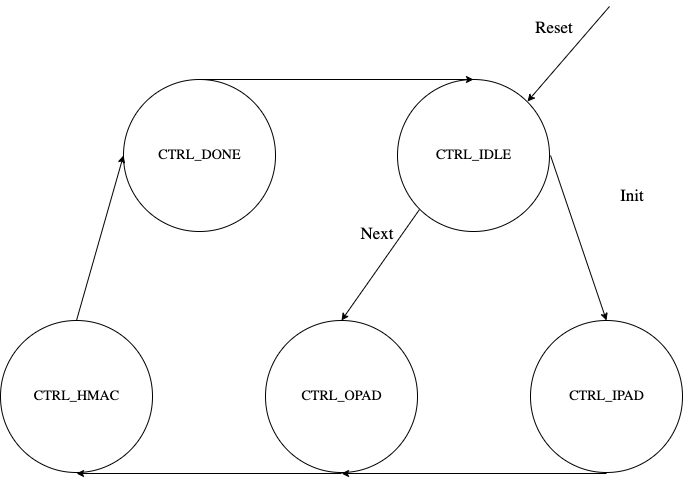

| 991 | 960 | The HMAC architecture has the finite-state machine as shown in the following figure. | |

| 992 | 961 | ||

| 993 | -*Figure 29: HMAC FSM* | ||

| 962 | +*Figure 30: HMAC FSM* | ||

| 994 | 963 | ||

| 995 | 964 |  | |

| 996 | 965 | ||

| 966 | +### CSR Mode | ||

| 967 | + | ||

| 968 | +When the CSR Mode register is set, the HMAC512 core uses the value latched from the cptra_csr_hmac_key interface pins in place of the API key register. These pins are latched internally after powergood assertion during DEVICE_MANUFACTURING lifecycle state. During debug mode operation this value is overridden with all 1's, and during any other lifecycle state it has a value of zero. | ||

| 969 | + | ||

| 997 | 970 | ### Signal descriptions | |

| 998 | 971 | ||

| 999 | 972 | The HMAC architecture inputs and outputs are described in the following table. | |

| 1000 | 973 | ||

| 1001 | 974 | | Name | Input or output | Description | | |

| 1002 | -| :----------------- | :-------------- | :----------- | | ||

| 975 | +| :-------------------------- | :-------------- | :----------- | | ||

| 1003 | 976 | | clk | input | All signal timings are related to the rising edge of clk. | | |

| 1004 | 977 | | reset_n | input | The reset signal is active LOW and resets the core. This is the only active LOW signal. | | |

| 1005 | 978 | | init | input | The core is initialized and processes the key and the first block of the message. | | |

| 1006 | 979 | | next | input | The core processes the rest of the message blocks using the result from the previous blocks. | | |

| 1007 | 980 | | zeroize | input | The core clears all internal registers to avoid any SCA information leakage. | | |

| 1008 | -| key\[383:0\] | input | The input key. | | ||

| 981 | +| csr_mode | input | When set, the key comes from the cptra_csr_hmac_key interface pins. This key is valid only during MANUFACTURING mode. | | ||

| 982 | +| mode | input | Indicates the hmac type of the function. This can be: <br>- HMAC384 <br>- HMAC512. | | ||

| 983 | +| cptra_csr_hmac_key\[511:0\] | input | The key to be used during csr mode. | | ||

| 984 | +| key\[511:0\] | input | The input key. | | ||

| 1009 | 985 | | block\[1023:0\] | input | The input padded block of message. | | |

| 1010 | -| LFSR_seed\[159:0\] | Input | The input to seed PRNG to enable the masking countermeasure for SCA protection. | | ||

| 986 | +| LFSR_seed\[383:0\] | Input | The input to seed PRNG to enable the masking countermeasure for SCA protection. | | ||

| 1011 | 987 | | ready | output | When HIGH, the signal indicates the core is ready. | | |

| 1012 | -| tag\[383:0\] | output | The HMAC value of the given key or block. For PRF-HMAC-SHA-384, a 384-bit tag is required. For HMAC-SHA-384-192, the host is responsible for reading 192 bits from the MSB. | | ||

| 988 | +| tag\[511:0\] | output | The HMAC value of the given key or block. For PRF-HMAC-SHA-512, a 512-bit tag is required. For HMAC-SHA-512-256, the host is responsible for reading 256 bits from the MSB. | | ||

| 1013 | 989 | | tag_valid | output | When HIGH, the signal indicates the result is ready. | | |

| 1014 | 990 | ||

| 1015 | 991 | ||

| @@ -1021,7 +997,7 @@ | |||

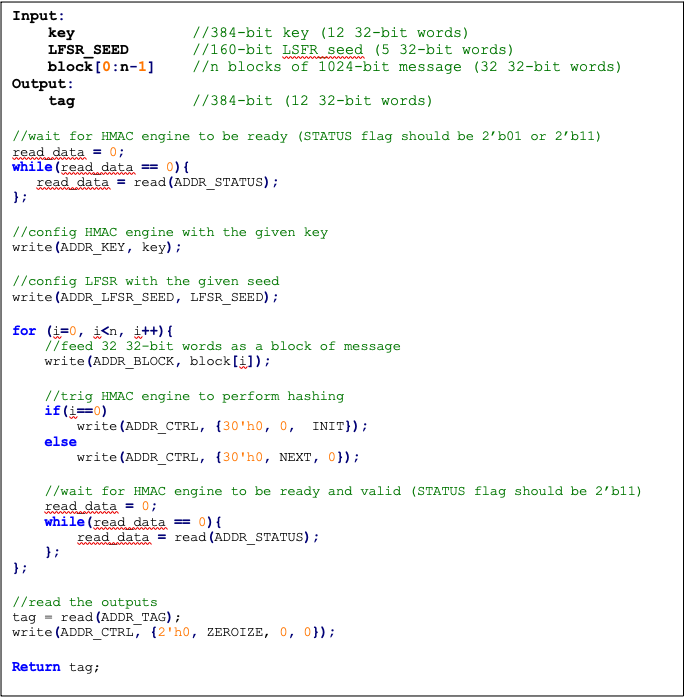

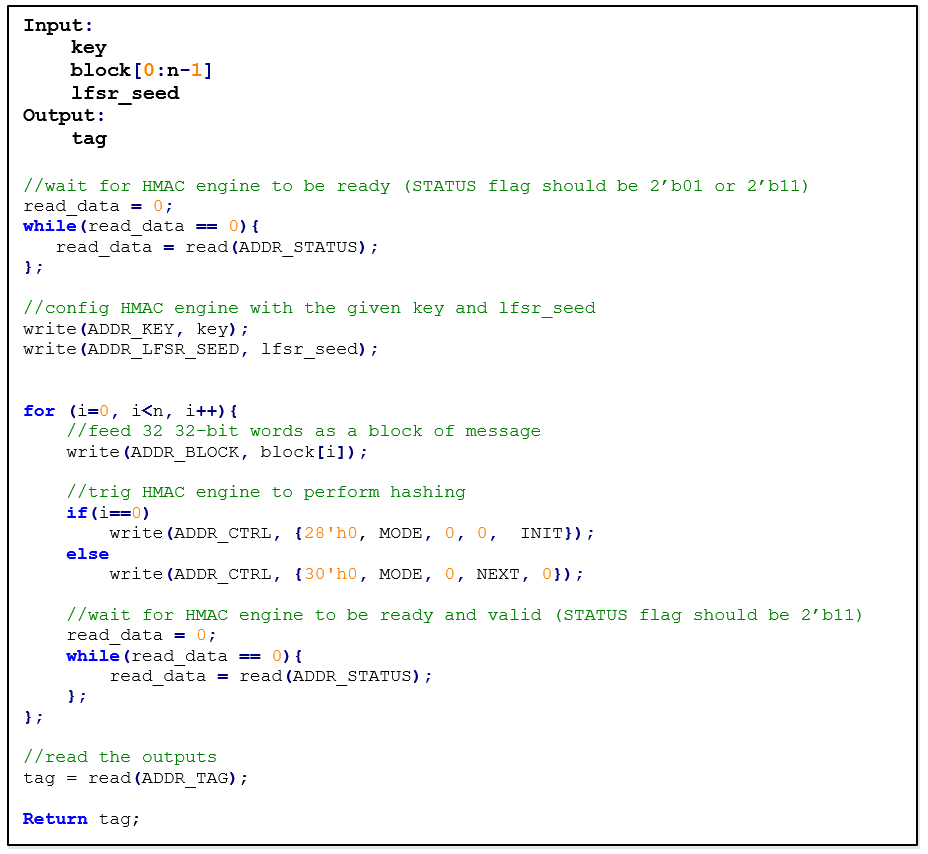

| 1021 | 997 | ||

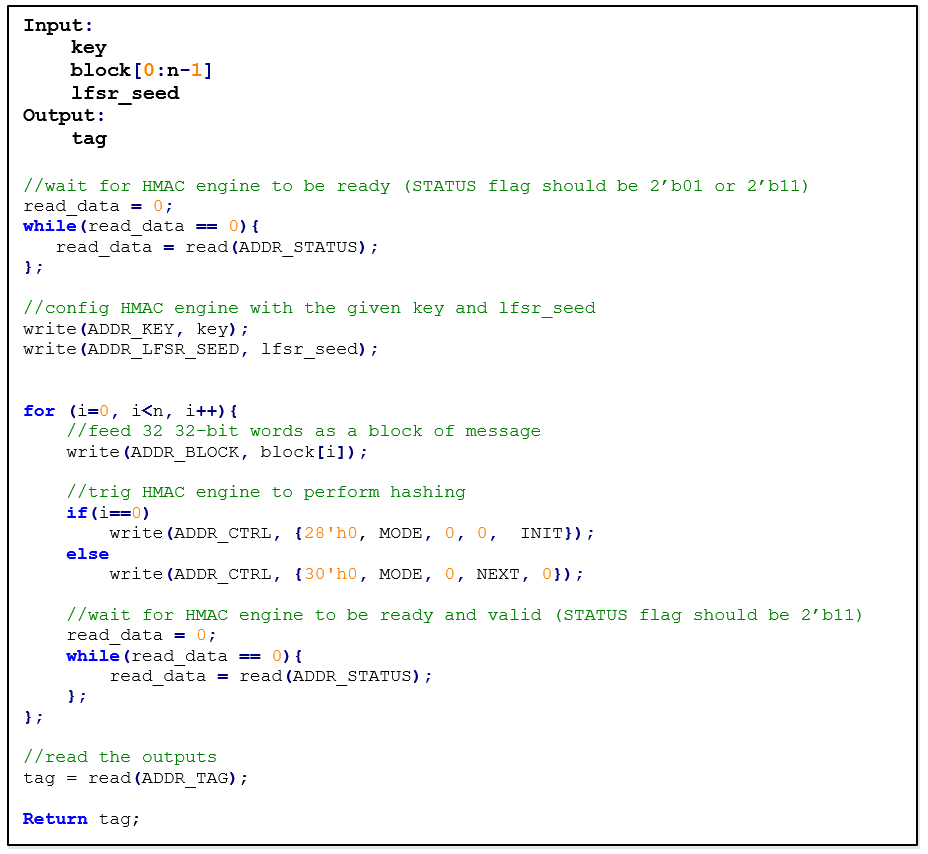

| 1022 | 998 | The following pseudocode demonstrates how the HMAC interface can be implemented. | |

| 1023 | 999 | ||

| 1024 | -*Figure 30: HMAC pseudocode* | ||

| 1000 | +*Figure 31: HMAC pseudocode* | ||

| 1025 | 1001 | ||

| 1026 | 1002 |  | |

| 1027 | 1003 | ||

| @@ -1033,7 +1009,7 @@ | |||

| 1033 | 1009 | ||

| 1034 | 1010 | The embedded countermeasures are based on "Differential Power Analysis of HMAC Based on SHA-2, and Countermeasures" by McEvoy et. al. To provide the required random values for masking intermediate values, a lightweight 74-bit LFSR is implemented. Based on “Spin Me Right Round Rotational Symmetry for FPGA-specific AES” by Wegener et. al., LFSR is sufficient for masking statistical randomness. | |

| 1035 | 1011 | ||

| 1036 | -Each round of SHA512 execution needs 6,432 random bits, while one HMAC operation needs at least 4 rounds of SHA512 operations. However, the proposed architecture requires only 160-bit LFSR seed and provides first-order DPA attack protection at the cost of 10% latency overhead with negligible hardware resource overhead. | ||

| 1012 | +Each round of SHA512 execution needs 6,432 random bits, while one HMAC operation needs at least 4 rounds of SHA512 operations. However, the proposed architecture requires only 384-bit LFSR seed and provides first-order DPA attack protection at the cost of 10% latency overhead with negligible hardware resource overhead. | ||

| 1037 | 1013 | ||

| 1038 | 1014 | ### Performance | |

| 1039 | 1015 | ||

| @@ -1054,9 +1030,9 @@ | |||

| 1054 | 1030 | | 128 KiB message | 207,979 | 519.947 | 1,923 | | |

| 1055 | 1031 | ||

| 1056 | 1032 | ||

| 1057 | -#### Hardware/software architecture | ||

| 1058 | - | ||

| 1059 | -In this architecture, the HMAC interface and controller are implemented in RISC-V core. The performance specification of the HMAC architecture is reported as shown in the following table. | ||

| 1033 | +#### Hardware/software architecture | ||

| 1034 | + | ||

| 1035 | +In this architecture, the HMAC interface and controller are implemented in RISC-V core. The performance specification of the HMAC architecture is reported as shown in the following table. | ||

| 1060 | 1036 | ||

| 1061 | 1037 | | Operation | Cycle count \[CCs\] | Time \[us\] @ 400 MHz | Throughput \[op/s\] | | |

| 1062 | 1038 | | :-------------------- | :------------------ | :-------------------- | :------------------ | | |

| @@ -1090,7 +1066,7 @@ | |||

| 1090 | 1066 | ||

| 1091 | 1067 | 1. Set V_init = 0x01 0x01 0x01 ... 0x01 (V has 384-bit) | |

| 1092 | 1068 | 2. Set K_init = 0x00 0x00 0x00 ... 0x00 (K has 384-bit) | |

| 1093 | - 3. K_tmp = HMAC(K_init, V_init || 0x00 || entropy || nonce) | ||

| 1069 | + 3. K_tmp = HMAC(K_init, V_init || 0x00 || entropy || nonce) | ||

| 1094 | 1070 | 4. V_tmp = HMAC(K_tmp, V_init) | |

| 1095 | 1071 | 5. K_new = HMAC(K_tmp, V_tmp || 0x01 || entropy || nonce) | |

| 1096 | 1072 | 6. V_new = HMAC(K_new, V_tmp) | |

| @@ -1138,13 +1114,15 @@ | |||

| 1138 | 1114 | ||

| 1139 | 1115 | ## ECC | |

| 1140 | 1116 | ||

| 1141 | -The ECC unit includes the ECDSA (Elliptic Curve Digital Signature Algorithm) engine, offering a variant of the cryptographically secure Digital Signature Algorithm (DSA), which uses elliptic curve (ECC). A digital signature is an authentication method in which a public key pair and a digital certificate are used as a signature to verify the identity of a recipient or sender of information. | ||

| 1117 | +The ECC unit includes the ECDSA (Elliptic Curve Digital Signature Algorithm) engine and the ECDH (Elliptic Curve Diffie-Hellman Key-Exchange) engine, offering a variant of the cryptographically secure Digital Signature Algorithm (DSA) and Diffie-Hellman Key-Exchange (DH), which uses elliptic curve (ECC). A digital signature is an authentication method in which a public key pair and a digital certificate are used as a signature to verify the identity of a recipient or sender of information. | ||

| 1142 | 1118 | ||

| 1143 | 1119 | The hardware implementation supports deterministic ECDSA, 384 Bits (Prime Field), also known as NIST-Secp384r1, described in RFC6979. | |

| 1144 | 1120 | ||

| 1121 | +The hardware implementation also supports ECDH, 384 Bits (Prime Field), also known as NIST-Secp384r1, described in SP800-56A. | ||

| 1122 | + | ||

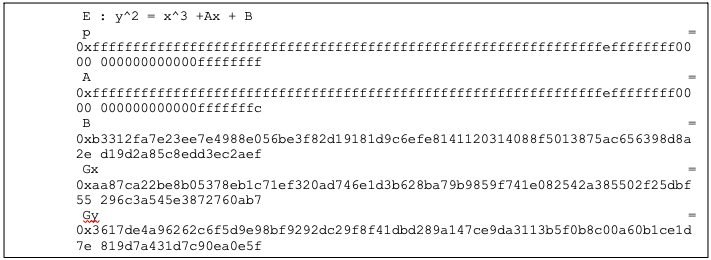

| 1145 | 1123 | Secp384r1 parameters are shown in the following figure. | |

| 1146 | 1124 | ||

| 1147 | -*Figure 31: Secp384r1 parameters* | ||

| 1125 | +*Figure 32: Secp384r1 parameters* | ||

| 1148 | 1126 | ||

| 1149 | 1127 |  | |

| 1150 | 1128 | ||

| @@ -1152,9 +1130,11 @@ | |||

| 1152 | 1130 | ||

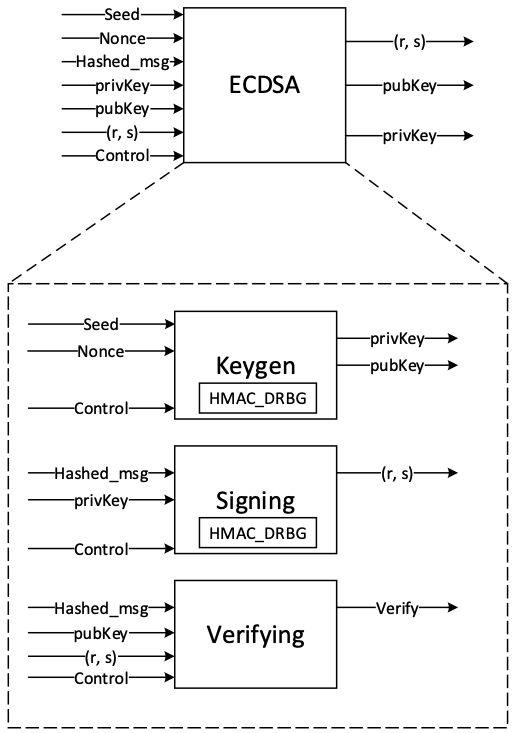

| 1153 | 1131 | The ECDSA consists of three operations, shown in the following figure. | |

| 1154 | 1132 | ||

| 1155 | -*Figure 32: ECDSA operations* | ||

| 1133 | +*Figure 33: ECDSA operations* | ||

| 1156 | 1134 | ||

| 1157 | 1135 |  | |

| 1136 | + | ||

| 1137 | +The ECDH also consists of the sharedkey generation. | ||

| 1158 | 1138 | ||

| 1159 | 1139 | #### KeyGen | |

| 1160 | 1140 | ||

| @@ -1166,7 +1146,7 @@ | |||

| 1166 | 1146 | ||

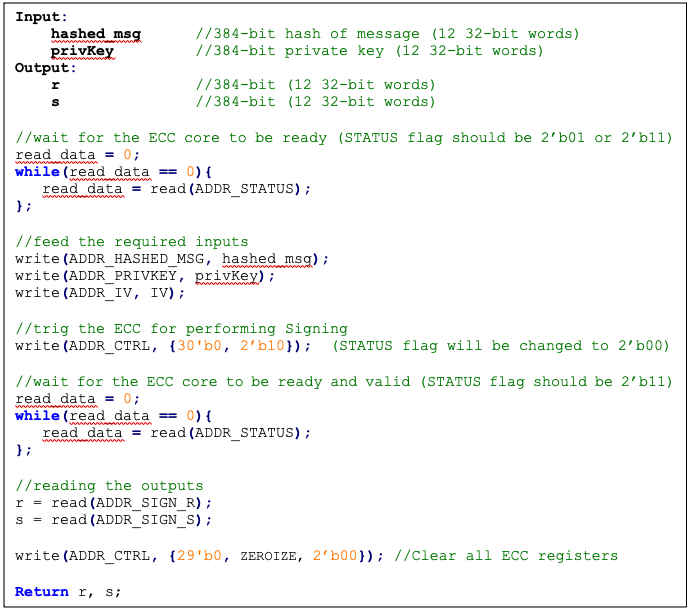

| 1167 | 1147 | #### Signing | |

| 1168 | 1148 | ||

| 1169 | -In the signing algorithm, a signature (r, s) is generated by Sign(privKey, h), taking a privKey and hash of message m, h = hash(m), using a cryptographic hash function, SHA384. The signing algorithm includes: | ||

| 1149 | +In the signing algorithm, a signature (r, s) is generated by Sign(privKey, h), taking a privKey and hash of message m, h = hash(m), using a cryptographic hash function, SHA512. The signing algorithm includes: | ||

| 1170 | 1150 | ||

| 1171 | 1151 | * Generate a random number k in the range [1..n-1], while k = HMAC\_DRBG(privKey, h) | |

| 1172 | 1152 | * Calculate the random point R = k × G | |

| @@ -1176,24 +1156,32 @@ | |||

| 1176 | 1156 | ||

| 1177 | 1157 | #### Verifying | |

| 1178 | 1158 | ||

| 1179 | -The signature (r, s) can be verified by Verify(pubKey ,h ,r, s) considering the public key pubKey and hash of message m, h=hash(m) using the same cryptographic hash function SHA384. The output is r’ value of verifying a signature. The ECDSA verify algorithm includes: | ||

| 1159 | +The signature (r, s) can be verified by Verify(pubKey ,h ,r, s) considering the public key pubKey and hash of message m, h=hash(m) using the same cryptographic hash function SHA512. The output is r’ value of verifying a signature. The ECDSA verify algorithm includes: | ||

| 1180 | 1160 | ||

| 1181 | 1161 | * Calculate s1 = s<sup>−1</sup> mod n | |

| 1182 | 1162 | * Compute R' = (h × s1) × G + (r × s1) × pubKey | |

| 1183 | 1163 | * Take r’ = R'x mod n, while R'x is x coordinate of R’=(R'x, R'y) | |

| 1184 | 1164 | * Verify the signature by comparing whether r' == r | |

| 1185 | 1165 | ||

| 1166 | +#### ECDH sharedkey | ||

| 1167 | + | ||

| 1168 | +In ECDH sharedkey generation, the shared key is generated by ECDH_sharedkey(privKey_A, pubKey_B), taking an own prikey and other party pubkey. The ECDH sharedkey algorithm is as follows: | ||

| 1169 | + | ||

| 1170 | +* Compute P = sharedkey(privkey_A, pubkey_b) where P(x,y) is a point on ECC. | ||

| 1171 | +* Output sharedkey = Px, where Px is x coordinate of P. | ||

| 1172 | + | ||

| 1173 | + | ||

| 1186 | 1174 | ### Architecture | |

| 1187 | 1175 | ||

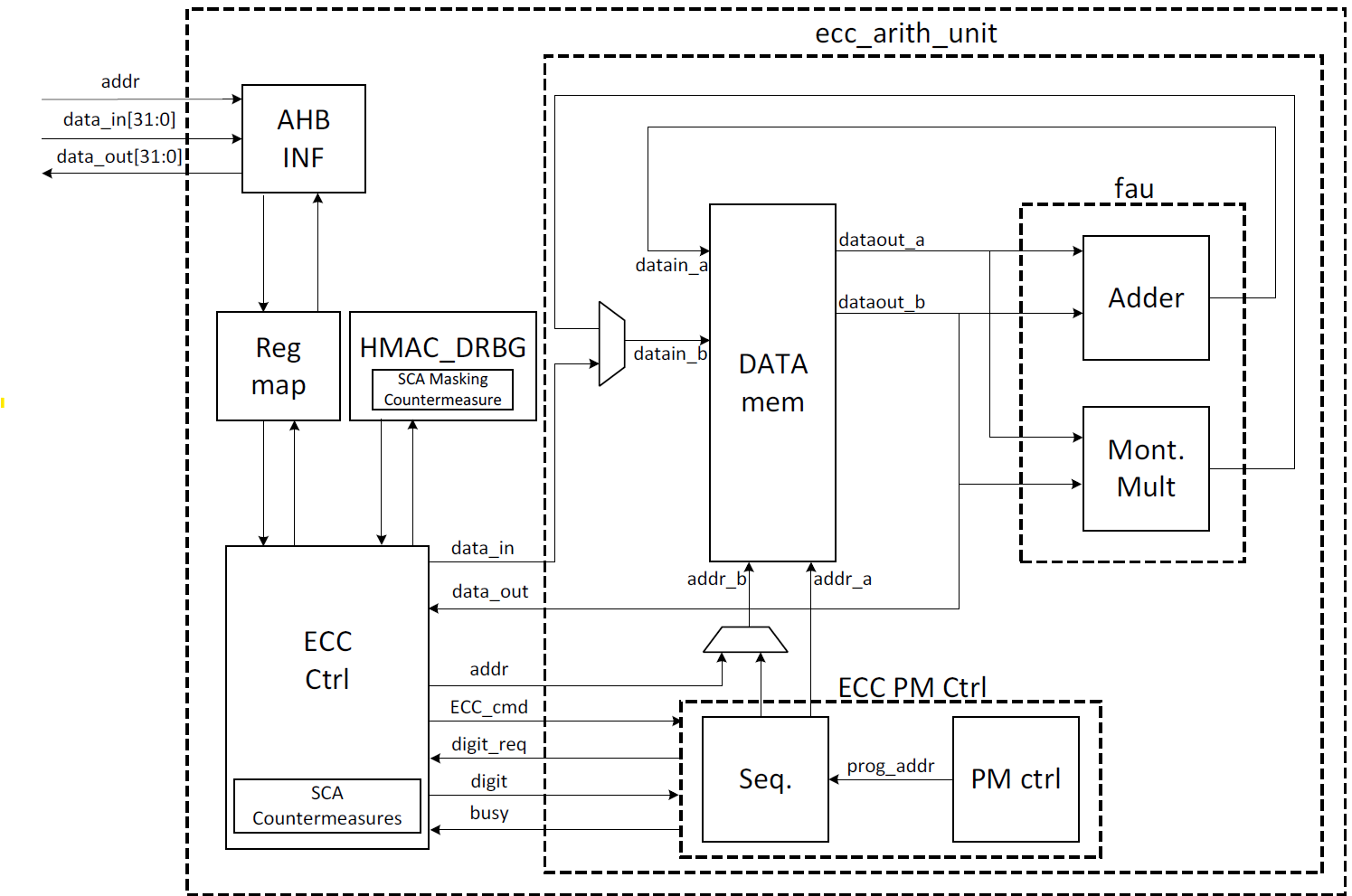

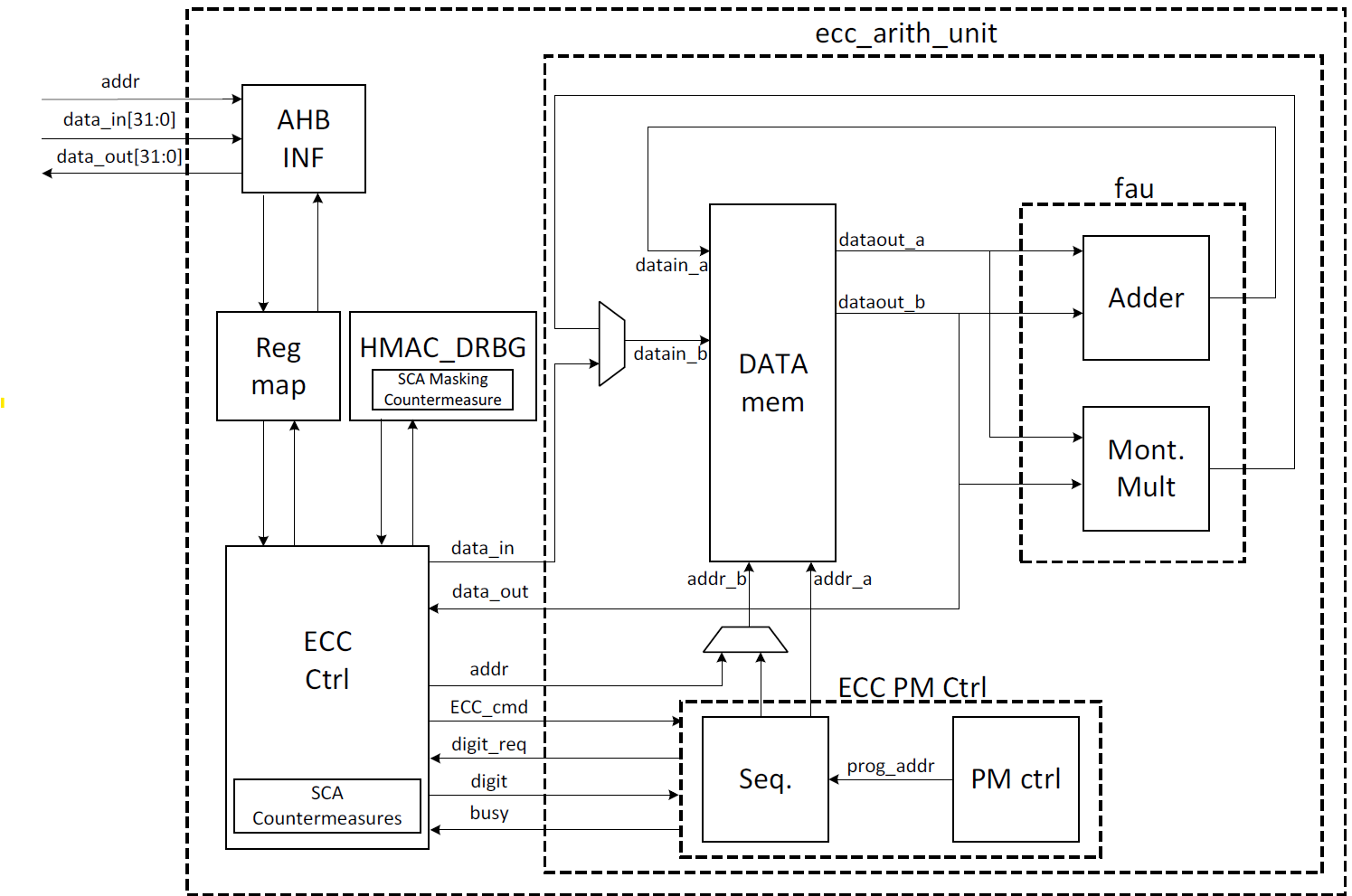

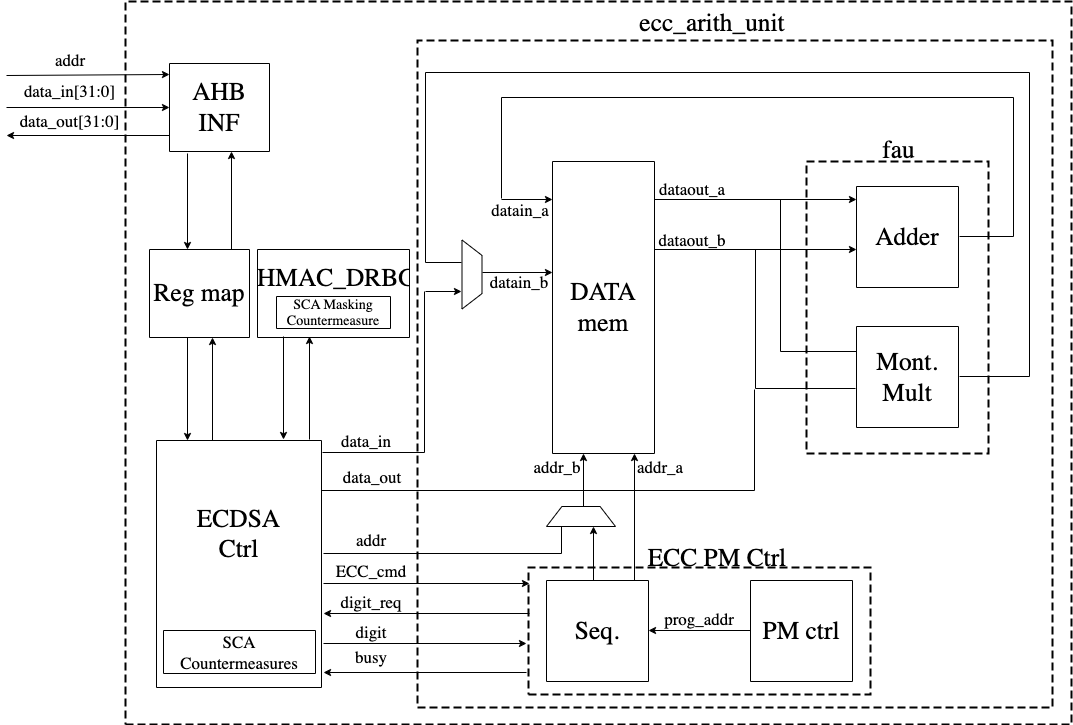

| 1188 | 1176 | The ECC top-level architecture is shown in the following figure. | |

| 1189 | 1177 | ||

| 1190 | -*Figure 33: ECDSA architecture* | ||

| 1191 | - | ||

| 1192 | - | ||

| 1178 | +*Figure 34: ECC architecture* | ||

| 1179 | + | ||

| 1180 | + | ||

| 1193 | 1181 | ||

| 1194 | 1182 | ### Signal descriptions | |

| 1195 | 1183 | ||

| 1196 | -The ECDSA architecture inputs and outputs are described in the following table. | ||

| 1184 | +The ECC architecture inputs and outputs are described in the following table. | ||

| 1197 | 1185 | ||

| 1198 | 1186 | ||

| 1199 | 1187 | | Name | Input or output | Description | | |

| @@ -1206,49 +1194,56 @@ | |||

| 1206 | 1194 | | nonce \[383:0\] | input | The deterministic nonce for HMAC_DRBG in the KeyGen operation. | | |

| 1207 | 1195 | | privKey_in\[383:0\] | input | The input private key used in the signing operation. | | |

| 1208 | 1196 | | pubKey_in\[1:0\]\[383:0\] | input | The input public key(x,y) used in the verifying operation. | | |

| 1209 | -| hashed_msg\[383:0\] | input | The hash of message using SHA384. | | ||

| 1197 | +| hashed_msg\[383:0\] | input | The hash of message using SHA512. | | ||

| 1210 | 1198 | | ready | output | When HIGH, the signal indicates the core is ready. | | |

| 1211 | 1199 | | privKey_out\[383:0\] | output | The generated private key in the KeyGen operation. | | |

| 1212 | 1200 | | pubKey_out\[1:0\]\[383:0\] | output | The generated public key(x,y) in the KeyGen operation. | | |

| 1213 | 1201 | | r\[383:0\] | output | The signature value of the given priveKey/message. | | |

| 1214 | 1202 | | s\[383:0\] | output | The signature value of the given priveKey/message. | | |

| 1215 | 1203 | | r’\[383:0\] | Output | The signature verification result. | | |

| 1204 | +| DH_sharedkey\[383:0\] | output | The generated shared key in the ECDH sharedkey operation. | | ||

| 1216 | 1205 | | valid | output | When HIGH, the signal indicates the result is ready. | | |

| 1217 | 1206 | ||

| 1218 | 1207 | ||

| 1219 | 1208 | ### Address map | |

| 1220 | 1209 | ||

| 1221 | -The ECDSA address map is shown here: [ecc\_reg — clp Reference (chipsalliance.github.io)](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.ecc_reg). | ||

| 1210 | +The ECC address map is shown here: [ecc\_reg — clp Reference (chipsalliance.github.io)](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.ecc_reg). | ||

| 1222 | 1211 | ||

| 1223 | 1212 | ### Pseudocode | |

| 1224 | 1213 | ||

| 1225 | -The following pseudocode blocks demonstrate example implementations for KeyGen, Signing, and Verifying. | ||

| 1214 | +The following pseudocode blocks demonstrate example implementations for KeyGen, Signing, Verifying, and ECDH sharedkey. | ||

| 1226 | 1215 | ||

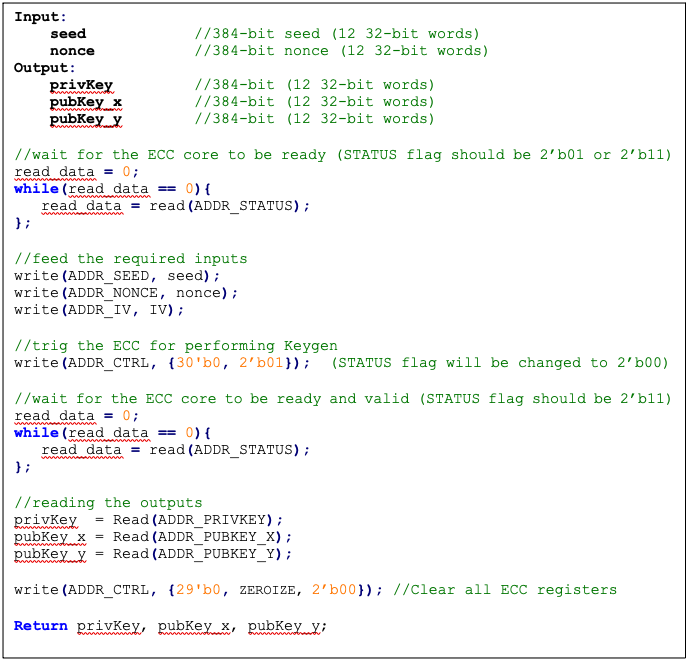

| 1227 | 1216 | #### KeyGen | |

| 1228 | 1217 | ||

| 1229 | -*Figure 34: KeyGen pseudocode* | ||

| 1218 | +*Figure 35: KeyGen pseudocode* | ||

| 1230 | 1219 | ||

| 1231 | 1220 |  | |

| 1232 | 1221 | ||

| 1233 | 1222 | #### Signing | |

| 1234 | 1223 | ||

| 1235 | -*Figure 35: Signing pseudocode* | ||

| 1224 | +*Figure 36: Signing pseudocode* | ||

| 1236 | 1225 | ||

| 1237 | 1226 |  | |

| 1238 | 1227 | ||

| 1239 | 1228 | #### Verifying | |

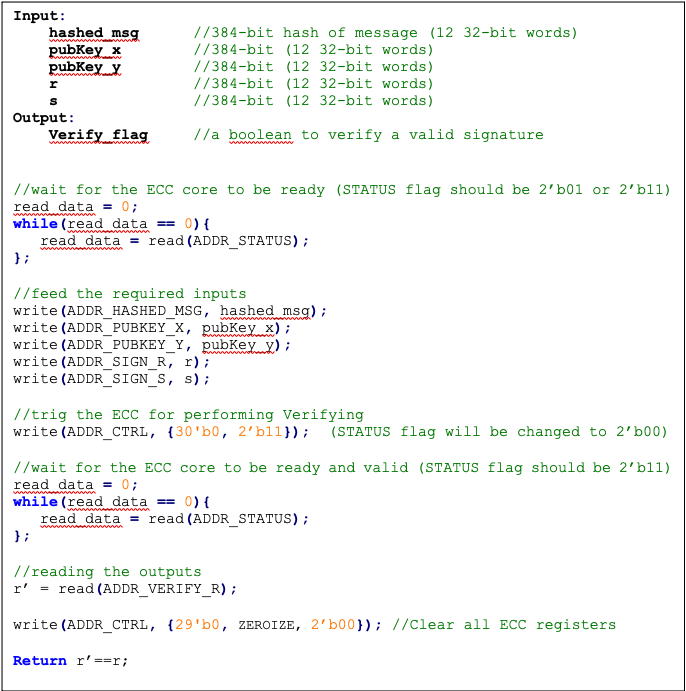

| 1240 | 1229 | ||

| 1241 | -*Figure 36: Verifying pseudocode* | ||

| 1230 | +*Figure 37: Verifying pseudocode* | ||

| 1242 | 1231 | ||

| 1243 | 1232 |  | |

| 1244 | 1233 | ||

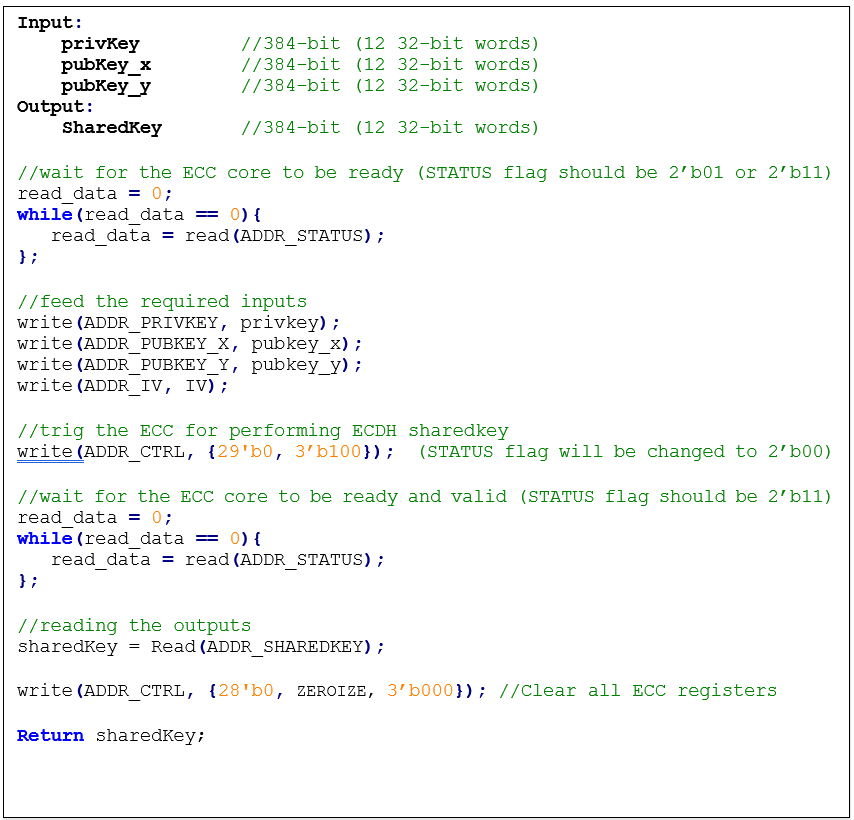

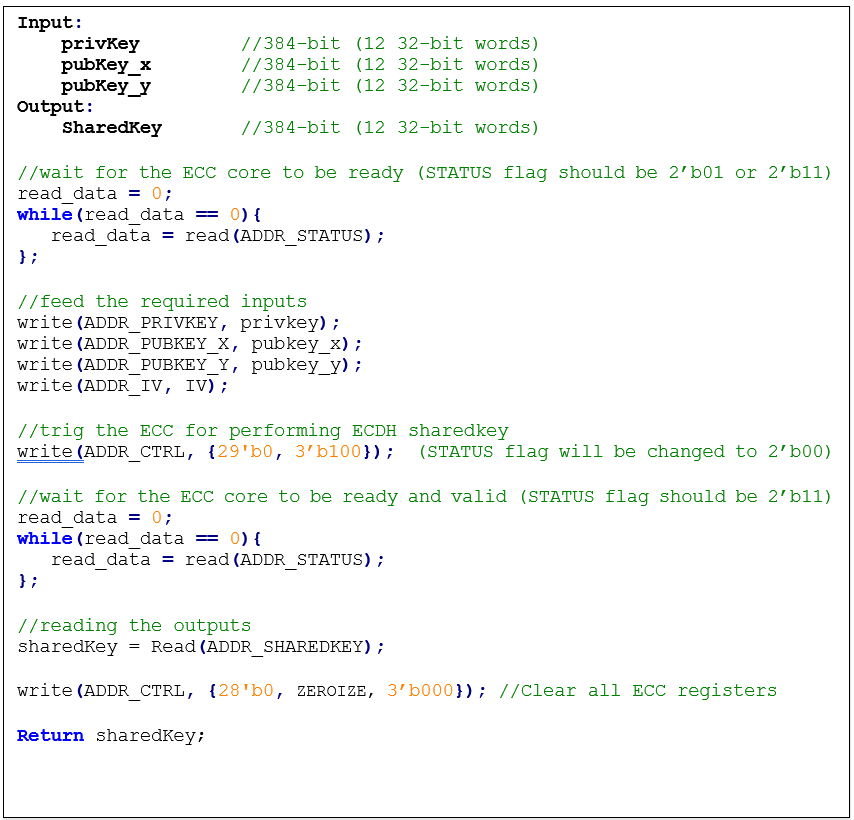

| 1234 | +#### ECDH sharedkey | ||

| 1235 | + | ||

| 1236 | +*Figure 38: ECDH sharedkey pseudocode* | ||

| 1237 | + | ||

| 1238 | + | ||

| 1239 | + | ||

| 1245 | 1240 | ### SCA countermeasure | |

| 1246 | 1241 | ||

| 1247 | -The described ECDSA has three main routines: KeyGen, Signing, and Verifying. Since the Verifying routine requires operation with public values rather than a secret value, our side-channel analysis does not cover this routine. Our evaluation covers the KeyGen and Signing routines where the secret values are processed. | ||

| 1248 | - | ||

| 1249 | -KeyGen consists of HMAC DRBG and scalar multiplication, while Signing first requires a message hashing and then follows the same operations as KeyGen (HMAC DRBG and scalar multiplication). The last step of Signing is generating “S” as the proof of signature. Since HMAC DRBG and hash operations are evaluated separately in our document, this evaluation covers scalar multiplication and modular arithmetic operations. | ||

| 1250 | - | ||

| 1251 | -#### Scalar multiplication | ||

| 1242 | +The described ECC has four main routines: KeyGen, Signing, Verifying, and ECDH sharedkey. Since the Verifying routine requires operation with public values rather than a secret value, our side-channel analysis does not cover this routine. Our evaluation covers the KeyGen, Signing, and ECDH sharedkey routines where the secret values are processed. | ||

| 1243 | + | ||

| 1244 | +KeyGen consists of HMAC DRBG and scalar multiplication, while Signing first requires a message hashing and then follows the same operations as KeyGen (HMAC DRBG and scalar multiplication). The last step of Signing is generating “S” as the proof of signature. Since HMAC DRBG and hash operations are evaluated separately in our document, this evaluation covers scalar multiplication and modular arithmetic operations. | ||

| 1245 | + | ||

| 1246 | +#### Scalar multiplication | ||

| 1252 | 1247 | ||

| 1253 | 1248 | To perform the scalar multiplication, the Montgomery ladder is implemented, which is inherently resistant to timing and single power analysis (SPA) attacks. | |

| 1254 | 1249 | ||

| @@ -1256,7 +1251,7 @@ | |||

| 1256 | 1251 | ||

| 1257 | 1252 | To protect the architecture against horizontal power/electromagnetic (EM) and differential power analysis (DPA) attacks, several countermeasures are embedded in the design [9]. Since these countermeasures require random inputs, HMAC-DRBG is fed by IV to generate these random values. | |

| 1258 | 1253 | ||

| 1259 | -Since HMAC-DRBG generates random value in a deterministic way, firmware MUST feed different IV to ECC engine for EACH keygen and signing operation. | ||

| 1254 | +Since HMAC-DRBG generates random value in a deterministic way, firmware MUST feed different IV to ECC engine for EACH keygen, signing, and ECDH sharedkey operation. | ||

| 1260 | 1255 | ||

| 1261 | 1256 | #### Base point randomization | |

| 1262 | 1257 | ||

| @@ -1284,7 +1279,7 @@ | |||

| 1284 | 1279 | ||

| 1285 | 1280 | Generating “S” as the proof of signature at the steps of the signing operation leaks where the hashed message is signed with private key and ephemeral key as follows: | |

| 1286 | 1281 | ||

| 1287 | -Since the given message is known or the signature part r is known, the attacker can perform a known-plaintext attack. The attacker can sign multiple messages with the same key, or the attacker can observe part of the signature that is generated with multiple messages but the same key. | ||

| 1282 | +Since the given message is known or the signature part r is known, the attacker can perform a known-plaintext attack. The attacker can sign multiple messages with the same key, or the attacker can observe part of the signature that is generated with multiple messages but the same key. | ||

| 1288 | 1283 | ||

| 1289 | 1284 | The evaluation shows that the CPA attack can be performed with a small number of traces, respectively. Thus, an arithmetic masked design for these operations is implemented. | |

| 1290 | 1285 | ||

| @@ -1292,7 +1287,7 @@ | |||

| 1292 | 1287 | ||

| 1293 | 1288 | This countermeasure is achieved by randomizing the privkey as follows: | |

| 1294 | 1289 | ||

| 1295 | -Although computation of “S” seems the most vulnerable point in our scheme, the operation does not have a big contribution to overall latency. Hence, masking these operations has low overhead on the cost of the design. | ||

| 1290 | +Although computation of “S” seems the most vulnerable point in our scheme, the operation does not have a big contribution to overall latency. Hence, masking these operations has low overhead on the cost of the design. | ||

| 1296 | 1291 | ||

| 1297 | 1292 | #### Random number generator for SCA countermeasure | |

| 1298 | 1293 | ||

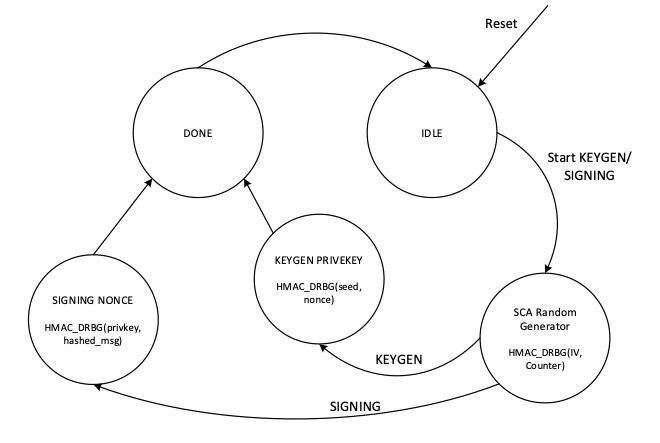

| @@ -1304,7 +1299,7 @@ | |||

| 1304 | 1299 | 2. KEYGEN PRIVKEY: Running HMAC\_DRBG with seed and nonce to generate the privkey in KEYGEN operation. | |

| 1305 | 1300 | 3. SIGNING NONCE: Running HMAC\_DRBG based on RFC6979 in SIGNING operation with privkey and hashed\_msg. | |

| 1306 | 1301 | ||

| 1307 | -*Figure 37: HMAC\_DRBG utilization* | ||

| 1302 | +*Figure 39: HMAC\_DRBG utilization* | ||

| 1308 | 1303 | ||

| 1309 | 1304 |  | |

| 1310 | 1305 | ||

| @@ -1320,7 +1315,7 @@ | |||

| 1320 | 1315 | ||

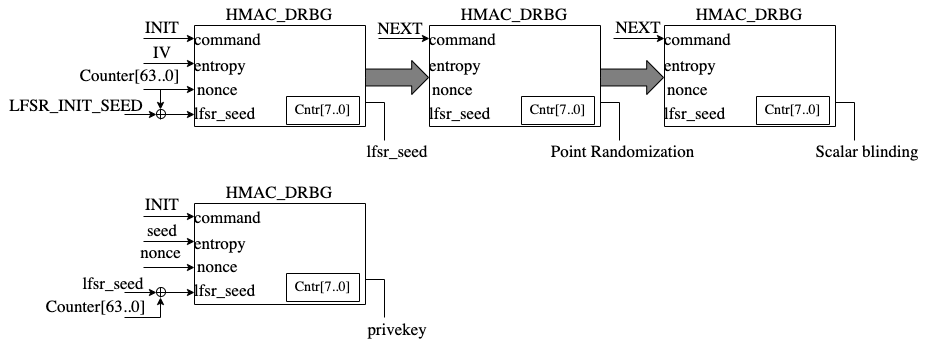

| 1321 | 1316 | The data flow of the HMAC\_DRBG operation in keygen operation mode is shown in the following figure. | |

| 1322 | 1317 | ||

| 1323 | -*Figure 38: HMAC\_DRBG data flow* | ||

| 1318 | +*Figure 40: HMAC\_DRBG data flow* | ||

| 1324 | 1319 | ||

| 1325 | 1320 |  | |

| 1326 | 1321 | ||

| @@ -1330,7 +1325,7 @@ | |||

| 1330 | 1325 | ||

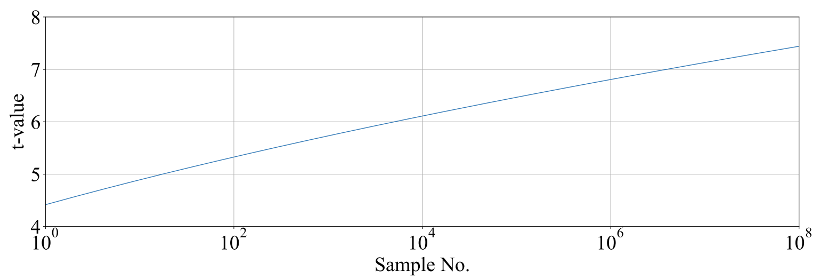

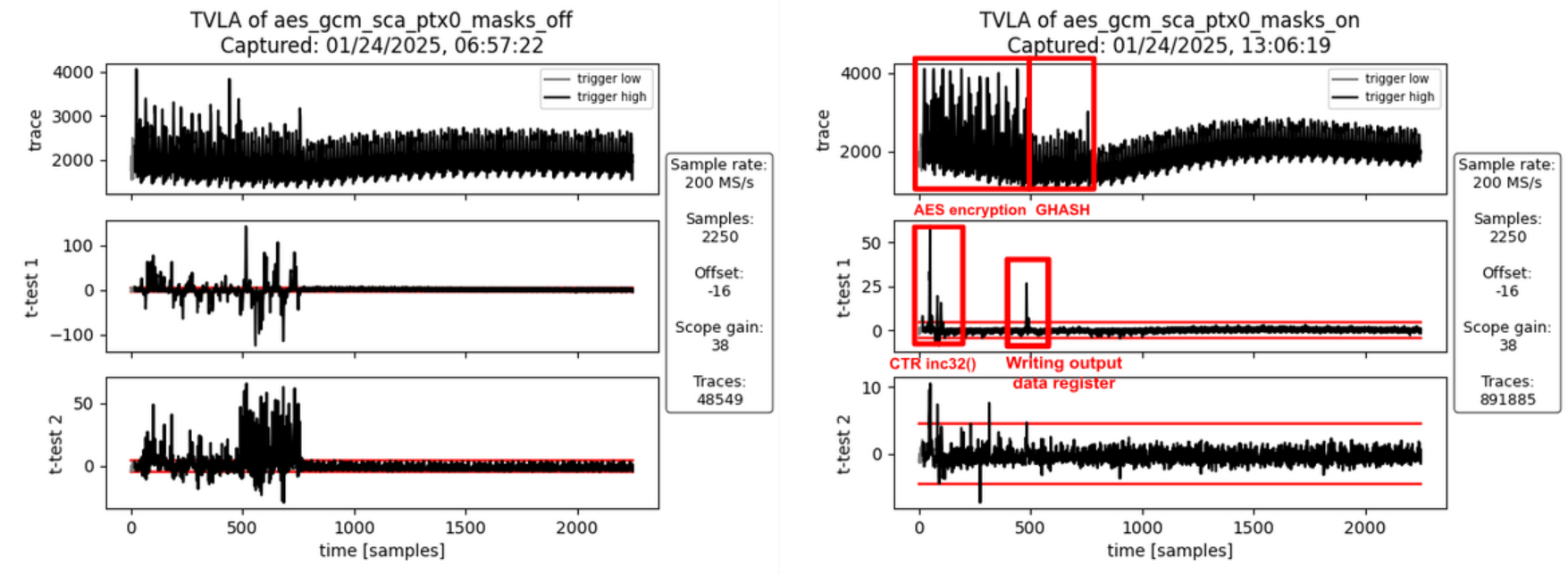

| 1331 | 1326 | In practice, observing a t-value greater than a specific threshold (mainly 4.5) indicates the presence of leakage. However, in ECC, due to its latency, around 5 million samples are required to be captured. This latency leads to many false positives and the TVLA threshold can be considered a higher value than 4.5. Based on the following figure from “Side-Channel Analysis and Countermeasure Design for Implementation of Curve448 on Cortex-M4” by Bisheh-Niasar et. al., the threshold can be considered equal to 7 in our case. | |

| 1332 | 1327 | ||

| 1333 | -*Figure 39: TVLA threshold as a function of the number of samples per trace* | ||

| 1328 | +*Figure 41: TVLA threshold as a function of the number of samples per trace* | ||

| 1334 | 1329 | ||

| 1335 | 1330 |  | |

| 1336 | 1331 | ||

| @@ -1340,7 +1335,7 @@ | |||

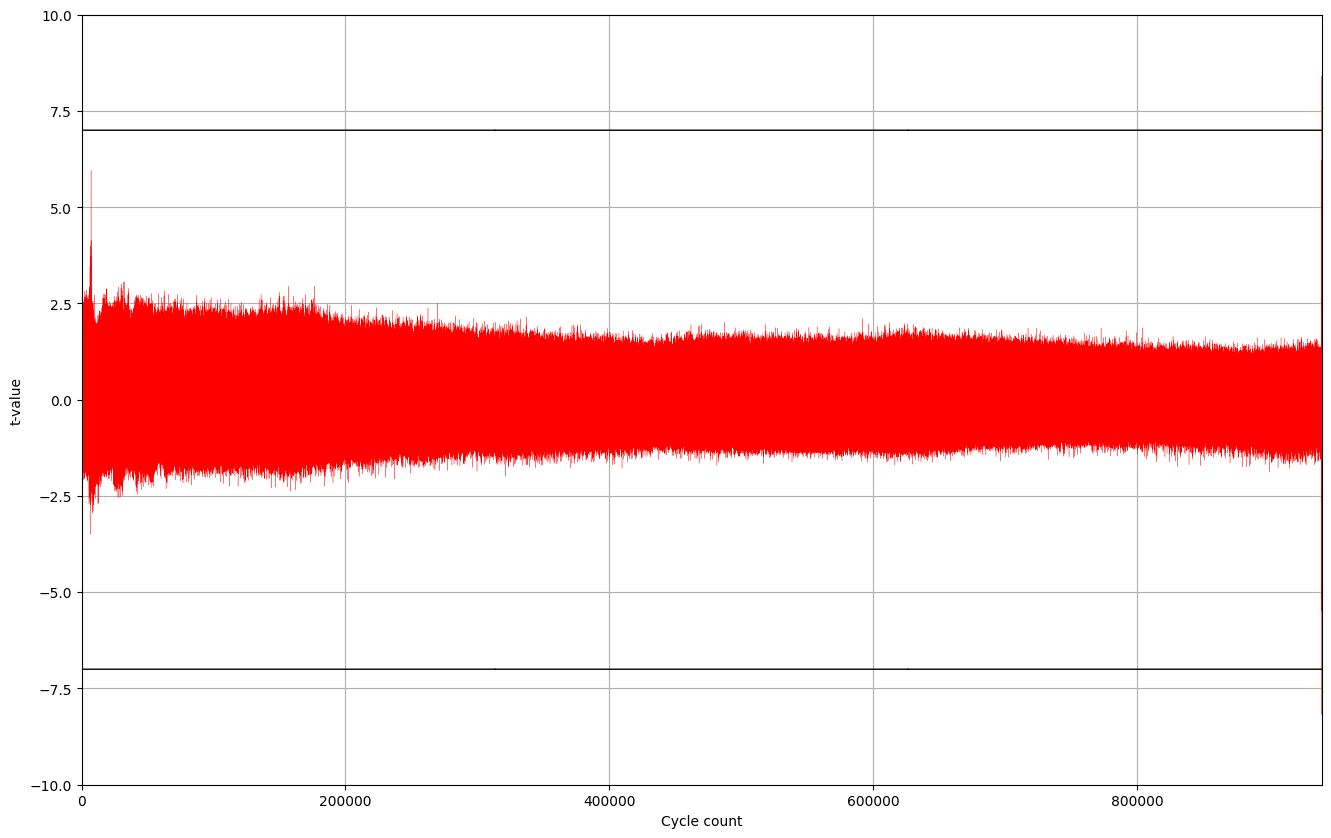

| 1340 | 1335 | The TVLA results for performing seed/nonce-dependent leakage detection using 200,000 traces is shown in the following figure. Based on this figure, there is no leakage in ECC keygen by changing the seed/nonce after 200,000 operations. | |

| 1341 | 1336 | ||

| 1342 | 1337 | ||

| 1343 | -*Figure 40: seed/nonce-dependent leakage detection using TVLA for ECC keygen after 200,000 traces* | ||

| 1338 | +*Figure 42: seed/nonce-dependent leakage detection using TVLA for ECC keygen after 200,000 traces* | ||

| 1344 | 1339 | ||

| 1345 | 1340 |  | |

| 1346 | 1341 | ||

| @@ -1348,13 +1343,13 @@ | |||

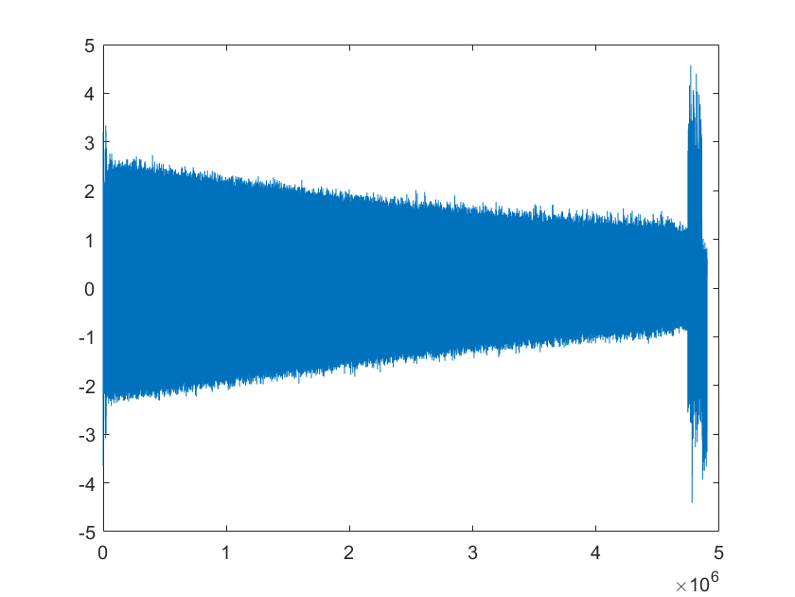

| 1348 | 1343 | ||

| 1349 | 1344 | The TVLA results for performing privkey-dependent leakage detection using 20,000 traces is shown in the following figure. Based on this figure, there is no leakage in ECC signing by changing the privkey after 20,000 operations. | |

| 1350 | 1345 | ||

| 1351 | -*Figure 41: privkey-dependent leakage detection using TVLA for ECC signing after 20,000 traces* | ||

| 1346 | +*Figure 43: privkey-dependent leakage detection using TVLA for ECC signing after 20,000 traces* | ||

| 1352 | 1347 | ||

| 1353 | 1348 |  | |

| 1354 | 1349 | ||

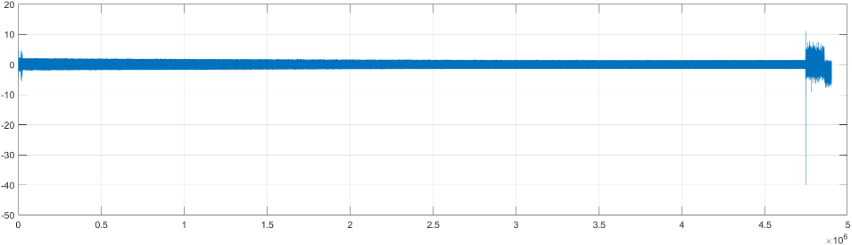

| 1355 | 1350 | The TVLA results for performing message-dependent leakage detection using 64,000 traces is shown in the following figure. Based on this figure, there is no leakage in ECC signing by changing the message after 64,000 operations. | |

| 1356 | 1351 | ||

| 1357 | -*Figure 42: Message-dependent leakage detection using TVLA for ECC signing after 64,000 traces* | ||

| 1352 | +*Figure 44: Message-dependent leakage detection using TVLA for ECC signing after 64,000 traces* | ||

| 1358 | 1353 | ||

| 1359 | 1354 |  | |

| 1360 | 1355 | ||

| @@ -1391,17 +1386,17 @@ | |||

| 1391 | 1386 | ||

| 1392 | 1387 | ## LMS Accelerator | |

| 1393 | 1388 | ||

| 1394 | -LMS cryptography is a type of hash-based digital signature scheme that was standardized by NIST in 2020. It is based on the Leighton-Micali Signature (LMS) system, which uses a Merkle tree structure to combine many one-time signature (OTS) keys into a single public key. LMS cryptography is resistant to quantum attacks and can achieve a high level of security without relying on large integer mathematics. | ||

| 1389 | +LMS cryptography is a type of hash-based digital signature scheme that was standardized by NIST in 2020. It is based on the Leighton-Micali Signature (LMS) system, which uses a Merkle tree structure to combine many one-time signature (OTS) keys into a single public key. LMS cryptography is resistant to quantum attacks and can achieve a high level of security without relying on large integer mathematics. | ||

| 1395 | 1390 | ||

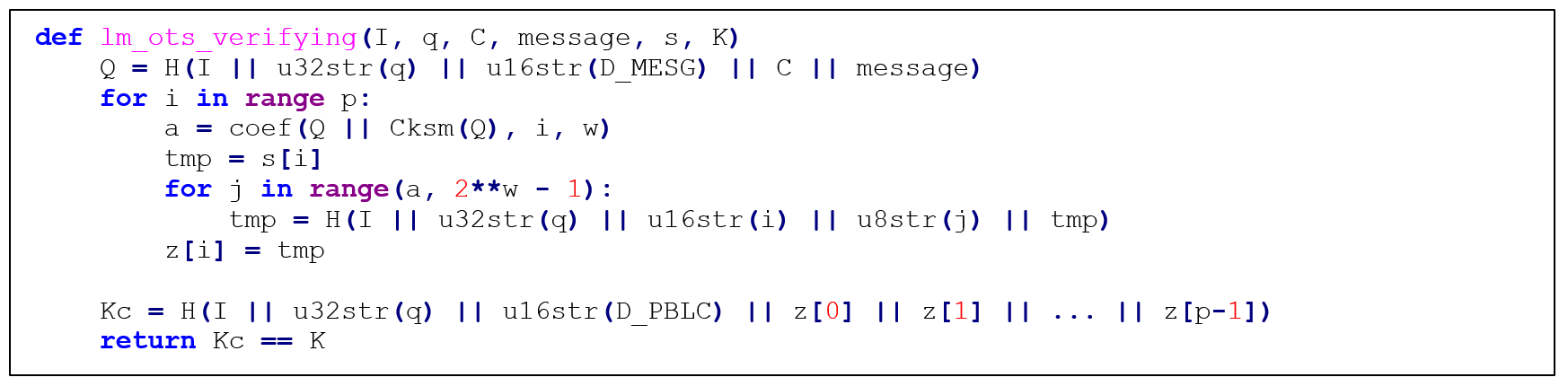

| 1396 | 1391 | Caliptra supports only LMS verification using a software/hardware co-design approach. Hence, the LMS accelerator reuses the SHA256 engine to speedup the Winternitz chain by removing software-hardware interface overhead. The LMS-OTS verification algorithm is shown in follwoing figure: | |

| 1397 | 1392 | ||

| 1398 | -*Figure 43: LMS-OTS Verification algorithm* | ||

| 1393 | +*Figure 45: LMS-OTS Verification algorithm* | ||

| 1399 | 1394 | ||

| 1400 | 1395 |  | |

| 1401 | 1396 | ||

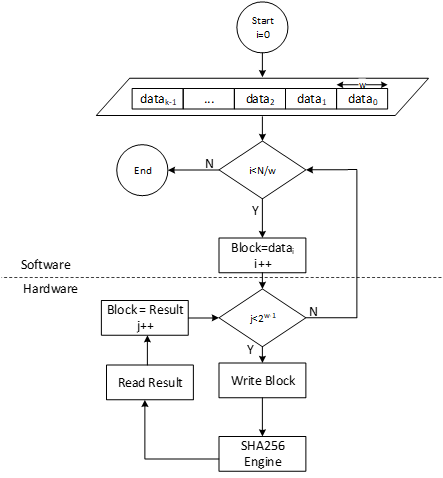

| 1402 | 1397 | The high-level architecture of LMS is shown in the following figure. | |

| 1403 | 1398 | ||

| 1404 | -*Figure 44: LMS high-level architecture* | ||

| 1399 | +*Figure 46: LMS high-level architecture* | ||

| 1405 | 1400 | ||

| 1406 | 1401 |  | |

| 1407 | 1402 | ||

| @@ -1426,7 +1421,7 @@ | |||

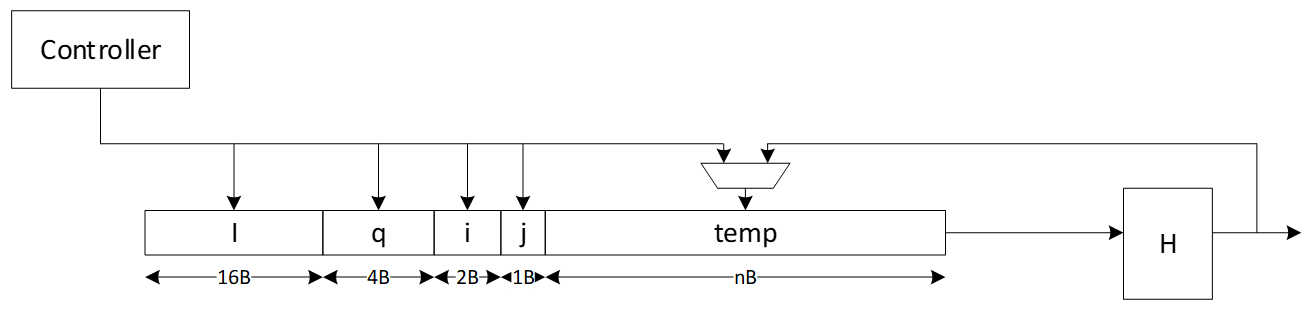

| 1426 | 1421 | ||

| 1427 | 1422 | The Winternitz hash chain can be accelerated in hardware to enhance the performance of the design. For that, a configurable architecture is proposed that can reuse SHA256 engine. The LMS accelerator architecture is shown in the following figure, while H is SHA256 engine. | |

| 1428 | 1423 | ||

| 1429 | -*Figure 45: Winternitz chain architecture* | ||

| 1424 | +*Figure 47: Winternitz chain architecture* | ||

| 1430 | 1425 | ||

| 1431 | 1426 |  | |

| 1432 | 1427 | ||

| @@ -1456,10 +1451,794 @@ | |||

| 1456 | 1451 | ||

| 1457 | 1452 | The address map for LMS accelerator integrated into SHA256 is shown here: [sha256\_reg — clp Reference (chipsalliance.github.io)](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.sha256_reg). | |

| 1458 | 1453 | ||

| 1454 | +## Adams Bridge - Dilithium (ML-DSA) | ||

| 1455 | + | ||

| 1456 | +Please refer to the [Adams-bridge specification](https://github.com/chipsalliance/adams-bridge/blob/main/docs/AdamsBridgeHardwareSpecification.md) | ||

| 1457 | + | ||

| 1458 | +### Address map | ||

| 1459 | +Address map of ML-DSA accelerator is shown here: [ML-DSA\_reg — clp Reference (chipsalliance.github.io)](https://chipsalliance.github.io/caliptra-rtl/main/internal-regs/?p=clp.mldsa_reg) | ||

| 1460 | + | ||

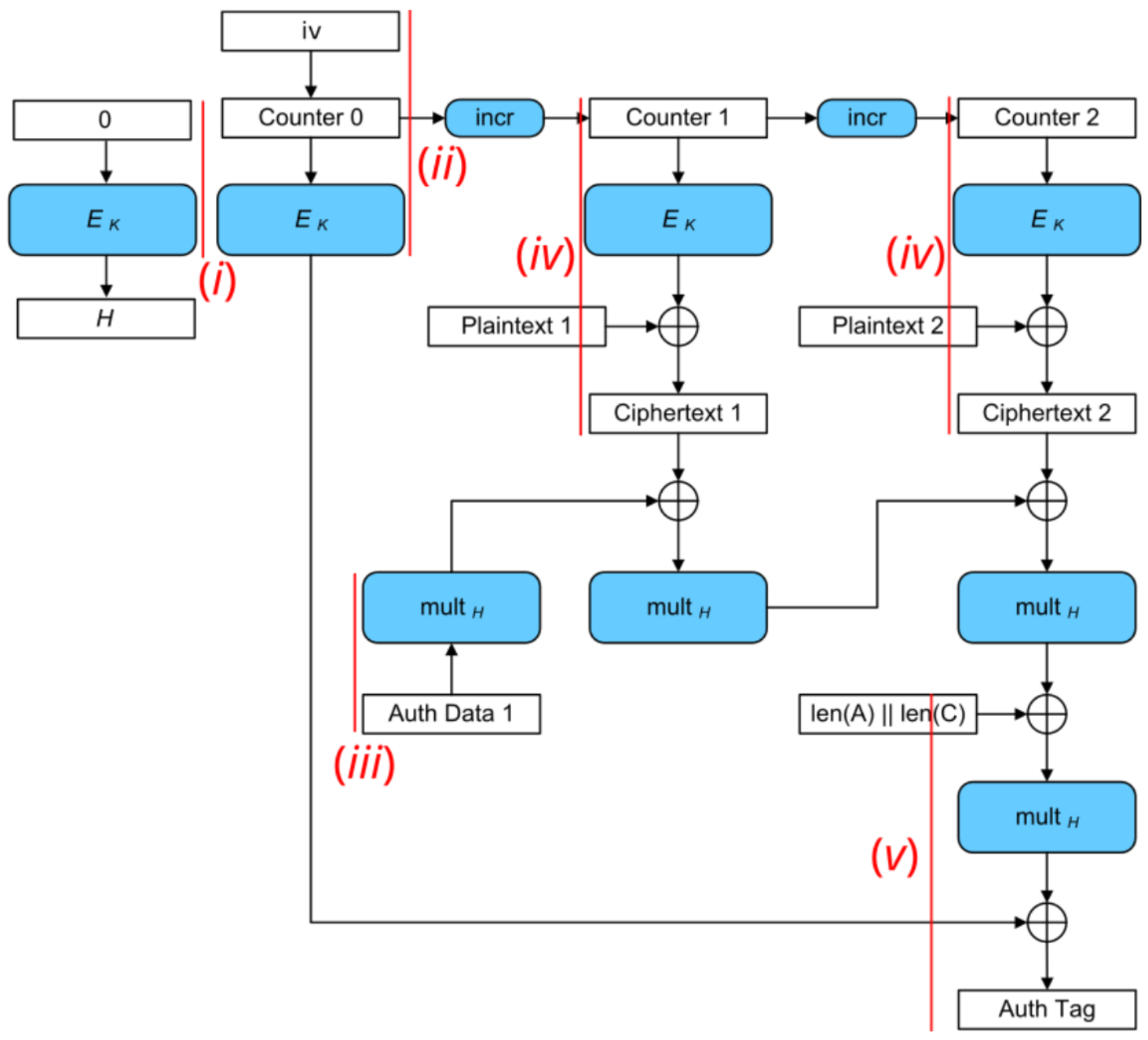

| 1461 | +## AES | ||

| 1462 | + | ||

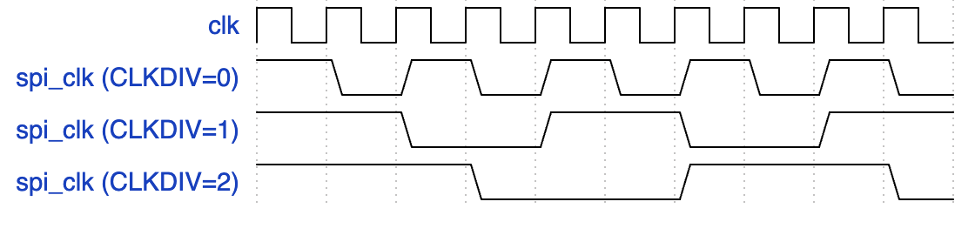

| 1463 | +The AES unit is a cryptographic accelerator that processes requests from the processor to encrypt or decrypt 16-byte data blocks. It supports AES-128/192/256 in various modes, including Electronic Codebook (ECB), Cipher Block Chaining (CBC), Cipher Feedback (CFB) with a fixed segment size of 128 bits (CFB-128), Output Feedback (OFB), Counter (CTR), and Galois/Counter Mode (GCM). | ||

| 1464 | + | ||

| 1465 | +The AES unit is reused from here, (see [aes](https://github.com/lowRISC/opentitan/tree/master/hw/ip/aes) with a shim to translate from AHB-lite to the tl-ul interface. | ||

| 1466 | + | ||

| 1467 | +Additional registers have been added to support key vault integration. Keys from the key vault can be loaded into the AES unit to be used for encryption or decryption. | ||

| 1468 | + | ||

| 1469 | +### Operation | ||

| 1470 | + | ||

| 1471 | +For more information, see the [AES Programmer's Guide](https://github.com/vogelpi/opentitan/blob/aes-gcm-review/hw/ip/aes/doc/programmers_guide.md). | ||

| 1472 | + | ||

| 1473 | +### Signal descriptions | ||

| 1474 | + | ||

| 1475 | +The AES architecture inputs and outputs are described in the following table. | ||

| 1476 | + | ||

| 1477 | +| Name | Input or output | Description | | ||

| 1478 | +| :--------------------------------- | :-------------- | :----------- | | ||

| 1479 | +| clk | input | All signal timings are related to the rising edge of clk. | | ||

| 1480 | +| reset_n | input | The reset signal is active LOW and resets the core. This is the only active LOW signal. | | ||

| 1481 | +| DATA_IN | input | Input block to be encrypted or decrypted. Written in four 32-bit registers. | | ||

| 1482 | +| DATA_OUT | output | Output block result of encryption or decryption. Stored in four 32-bit registers. | | ||

| 1483 | +| CTRL_SHADOWED.MANUAL_OPERATION | input | Configures the AES core to operation in manual mode. | | ||

| 1484 | +| CTRL_SHADOWED.PRNG_RESEED_RATE | input | Configures the rate of reseeding the internal PRNG used for masking. | | ||

| 1485 | +| CTRL_SHADOWED.SIDELOAD | input | When asserted, AES core will use the key from the keyvault interface. | | ||

| 1486 | +| CTRL_SHADOWED.KEY_LEN | input | Configures the AES key length. Supports 128, 192, and 256-bit keys. | | ||

| 1487 | +| CTRL_SHADOWED.MODE | input | Configures the AES block cipher mode. | | ||

| 1488 | +| CTRL_SHADOWED.OPERATION | input | Configures the AES core to operate in encryption or decryption modes. | | ||

| 1489 | +| CTRL_GCM_SHADOWED.PHASE | input | Configures the GCM phase. | | ||

| 1490 | +| CTRL_GCM_SHADOWED.NUM_VALID_BYTES | input | Configures the number of valid bytes of the current input block in GCM. | | ||

| 1491 | +| TRIGGER.PRNG_RESEED | input | Forces a PRNG reseed. | | ||

| 1492 | +| TRIGGER.DATA_OUT_CLEAR | input | Clears the DATA_OUT registers with pseudo-random data. | | ||

| 1493 | +| TRIGGER.KEY_IV_DATA_IN_CLEAR | input | Clears the Key, IV, and DATA_INT registers with pseudo-random data. | | ||

| 1494 | +| TRIGGER.START | input | Triggers the encryption/decryption of one data block if in manual operation mode. | | ||

| 1495 | +| STATUS.ALERT_FATAL_FAULT | output | A fatal fault has ocurred and the AES unit needs to be reset. | | ||

| 1496 | +| STATUS.ALERT_RECOV_CTRL_UPDATE_ERR | output | An update error has occurred in the shadowed Control Register. AES operation needs to be restarted by re-writing the Control Register. | | ||

| 1497 | +| STATUS.INPUT_READY | output | The AES unit is ready to receive new data input via the DATA_IN registers. | | ||

| 1498 | +| STATUS.OUTPUT_VALID | output | The AES unit has alid output data. | | ||